日時

場所

主催

共催

講演

Dr. Kunihiko Iizuka

SHARP Corporation, SSCS Kansai Chapter Chair

Lecture 1

Lecture 1

Prof. Kofi Makinwa, Delft University of Technology

Topic: Smart CMOS Sensors PDF(2.21MB)

Abstract: A smart sensor consists of a sensor and its interface electronics in the same package. Due to the low-level output of most sensors, designing interface electronics that “does no harm,” is quite challenging, especially in CMOS processes, whose precision is limited by 1/f noise and component mismatch. This talk will discuss the use of dynamic techniques such as dynamic element matching, switched-capacitor filtering and sigma-delta modulation in the design and realization of state-of-the-art smart CMOS sensors.

Prof. Bram Nauta, University of Twente

Topic: Analog and RF Circuit Techniques in Nanometer CMOS PDF(2.24MB)

Abstract: The BLIXER is a combination of Balun, LNA and Mixer, in one. The circuit features the cancelling of thermal noise coming from the input matching-transistor. This compact circuit enables down-conversion over a wide RF (0-7GHz) band at low noise (NF<5dB).

Abstract: The BLIXER is a combination of Balun, LNA and Mixer, in one. The circuit features the cancelling of thermal noise coming from the input matching-transistor. This compact circuit enables down-conversion over a wide RF (0-7GHz) band at low noise (NF<5dB).An interferer-robust receiver for wideband RF signals. (e.g. TV tuner or cognitive radio receiver) In this new concept, the harmonic rejection of a wideband receiver is improved by 20dB to 60dB using a 2-stage harmonic cancellation scheme. The 2-stage technique is highly insensitive for component accuracies and no trimming or calibration is therefore needed. Also thanks to an impedance up-conversion technique, the filter requirements at RF are strongly relaxed. Also a digital technique is introduced to achieve even 80dB harmonic rejection at the strongest interferer, making use of the same analog hardware....

Lecture 3

Lecture 3

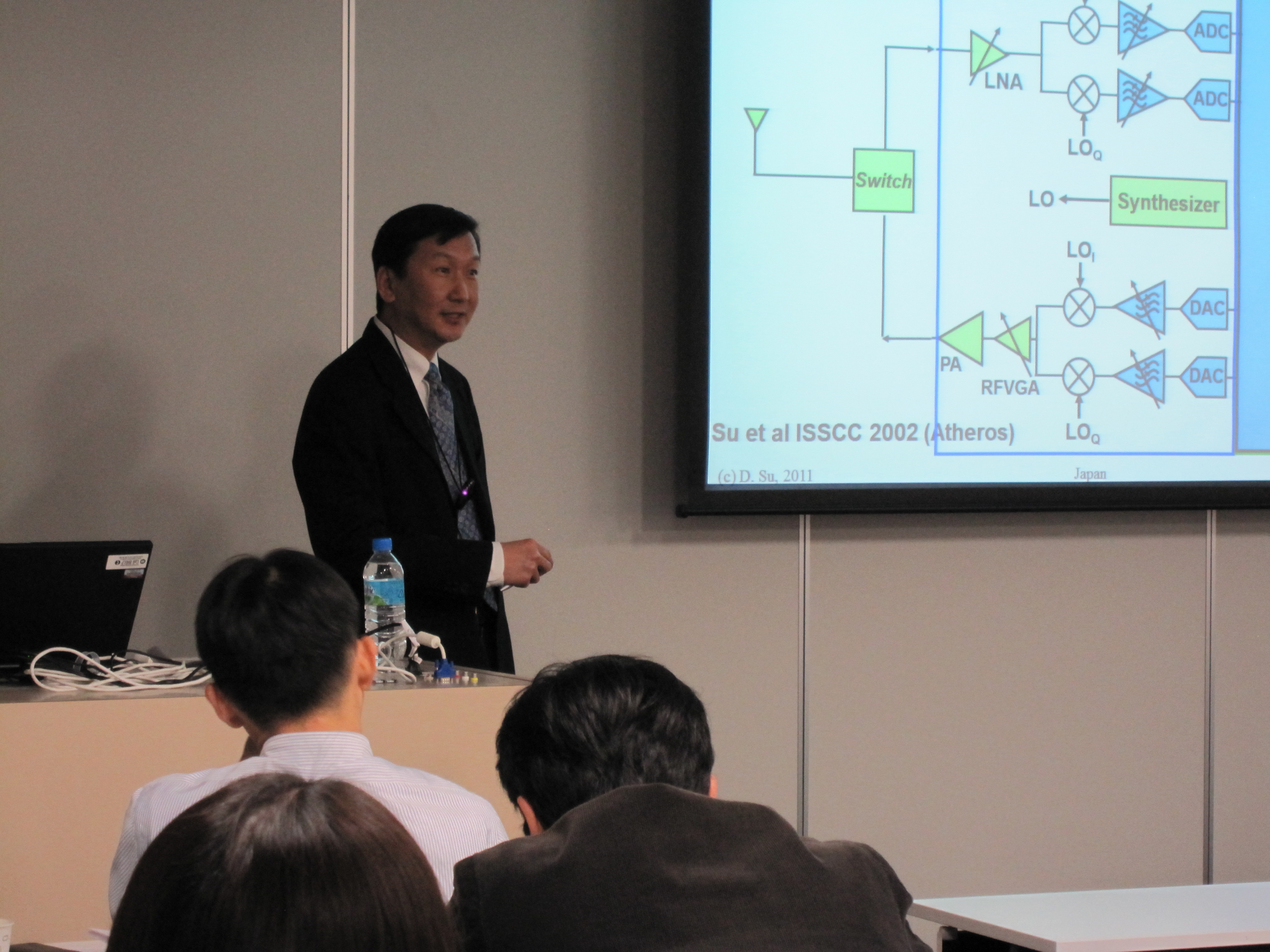

Dr. David Su, Qualcomm Incorporated

Topic: Challenges in Designing CMOS Wireless System-on-a-chip PDF(2.67MB)

Abstract: This talk describes the challenges in designing CMOS systems-on-a-chip for wireless communications. RF transceiver building blocks for signal amplification, frequency translation, and frequency selectivity are examined with special emphasis on low noise amplifier, power amplifier, mixer, and frequency synthesizer. System-on-a-chip integration issues are also discussed.

Prof. Minoru Fujishima, Hiroshima University

Topic: Millimeter-wave and Terahertz CMOS Design PDF(2.71MB)

Abstract: Millimeter-wave and its higher-frequency part “terahertz” have attracted many attentions to open up new applications such as ultrahigh-speed wireless communication and noninvasive transparent image. Utilizing recent transistor performance in CMOS technology, those new applications are being realized by commercial CMOS process. Since base-band signal processors are indispensable in a system level, CMOS circuits for millimeter-wave and terahertz have advantage against compound-semiconductor circuits from viewpoint of high-volume production and low-power consumption. In this talk, we will discuss millimeter-wave and terahertz CMOS design by clarifying difference from conventional microwave design. Design examples from system level to building block for mobile high-speed communication are also discussed.

Abstract: Millimeter-wave and its higher-frequency part “terahertz” have attracted many attentions to open up new applications such as ultrahigh-speed wireless communication and noninvasive transparent image. Utilizing recent transistor performance in CMOS technology, those new applications are being realized by commercial CMOS process. Since base-band signal processors are indispensable in a system level, CMOS circuits for millimeter-wave and terahertz have advantage against compound-semiconductor circuits from viewpoint of high-volume production and low-power consumption. In this talk, we will discuss millimeter-wave and terahertz CMOS design by clarifying difference from conventional microwave design. Design examples from system level to building block for mobile high-speed communication are also discussed.

Prof. Minoru Fujishima

Hiroshima University, SSCS Kansai Chapter Vice Chair

参加

人数

人数

集合

写真

写真