#### IEEE Donald O. Pederson Award 受賞記念講演

#### A/D変換器開発の歴史とその発展

松澤昭

IEEE Life Fellow 東京科学大学 名誉教授 (株) テックイデア 代表取締役

#### 2022 IEEE Donald O. Pederson Awardの受賞

#### 「デジタルビデオ機器用システムLSIに向けた 低電力A/D変換器開発の先駆的な貢献」

- 1. デジタルTV・ビデオシステム実現のためのバイポーラADCの開発

- 2. 超低電力CMOS ADCの開発とローパワーエレクトロニクスの振興

- 3. 低電力超高速ADCの開発とアナログ・デジタル混載システムLSIの開発

- 4. ミリ波CMOSトランシーバの開発

IEEE Donald O. Pederson Award in Solid-State CircuitsはIEEEのTechnical Field Awardの一つで、集積回路分野における社会への貢献、技術進歩への貢献、専門的なリーダーシップが顕著な個人、または3人までのチームに授与されるものである。1988年創設のIEEE Solid-State Circuits Award を継承し、2005年に現在の名前に改名された。

## 略歴

- ・1952年 秋田県に生まれる

- ・1978年 東北大学大学院工学研究科 修士課程修了 松下電器産業(現パナソニック) 入社 以後,中央研究所,半導体開発本部などでA/D変換器を中心とする デジタル電子機器用アナ・デジ混載LSIの開発および低電力LSI技術の開発に従事

- ·1997年 博士(工学:東北大学)GM(部長職)

- ・2002年 IEEE Fellow

- ・2003年 松下電器産業退職 東京工業大学大学院工学研究科教授

- ・2018年 東京工業大学退職 東京工業大学名誉教授 (株) テックイデア 代表取締役

- ・2022年 IEEE Donald. O. Pederson Award 受賞

- ・2023年 IEEE Life Fellow

### 発表内容

- ・A/D変換器の概要

- ・バイポーラADC:HDTVとフラッシュADC

- ・バイCMOS ADC: HDTVと2ステップフラッシュADC

- ・CMOS ADC:デジタルハンディーカムと容量補間型ADC

- ・ローパワーエレクトロニクス:腕時計型PHSと自然エネルギーPDA

- ・アナ・デジ混載システムLSI:DVDとワンチップアナ・デジ混載SoC

- SAR ADCの革新:光通信とSAR ADC

- ・アナログコンピュータ:電荷保存則を用いた超低エネルギーAI演算器

- ・まとめ

#### 発表の要旨

電子機器の発展と変遷および、バイポーラ、Bi-CMOS, CMOSなどのデバイスの変遷に伴うADC技術の歴史と発展について概観する。

連続時間型アナログ回路から離散時間型アナログ回路へ、更に定常電流が流れず超低エネルギーで動作するダイナミック型アナログ回路への変遷を示す。

素子面積の縮小と精度の関係、精度確保のためのチョッパーや補間技術、キャリブレーション技術。DVDのワンチップアナ・デジ混載システムLSIを可能にした超高速ADCの低電力技術について述べる。

更に超高速デジタル光通信を可能にした100GS/sインターリーブ逐次比較型ADCを例に取り、 CMOSロジック回路のようにスケーリング則が適用可能で、微細化により一層の高速化と低 電力化が図れるADC技術について紹介する。

最後にAIや量子コンピュータという先端アナログコンピュータ技術にとってもADC技術が重要であることを示す。

# 包括的な参考文献

#### 個別の技術に関しては、各スライドに簡単な参考文献を示したが、 包括的な文献を以下に示す

- A. Matsuzawa, "A Brief History of Nyquist Analog-to-Digital Converters" IEICE TRANSACTIONS on Electronics Vol.E106-C No.10 pp.493-505

- Life and Times of Akira Matsuzawa: In his own words, IEEE SSCS magazine Volume: 14, Issue: 1, winter 2022.

- A. Matsuzawa "Shape the World with Mixed-Signal Integrated Circuits Past, Present, and Future", 2023 IEEE International Solid-State Circuits Conference (ISSCC)

- A. Matsuzawa, "Sampling circuit issues in A/D converters and challenges for the solution", IEICE Electronics Express, 2023

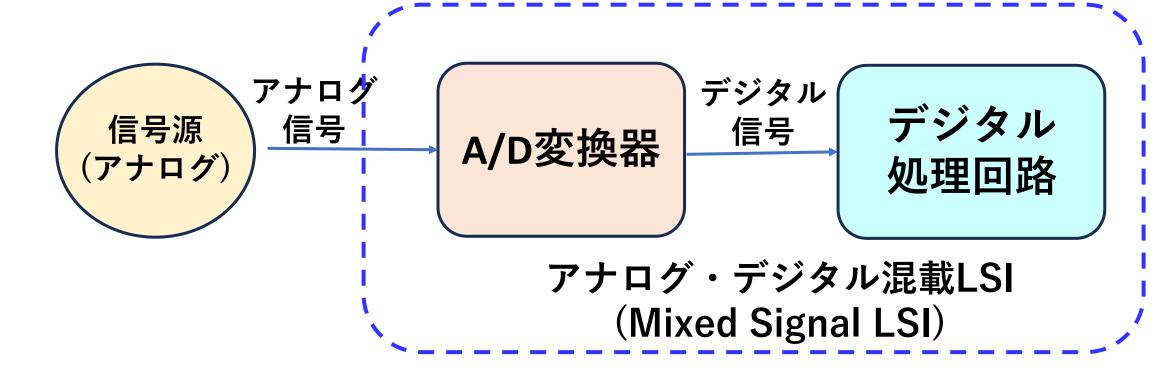

## A/D変換器開発の背景

電子機器はアナログからデジタルに進化したが、信号源はアナログであり、デジタル信号に変換するためA/D変換器 (ADC)が必要とされる。ADCはデジタル環境にはあるもののアナログ技術をベースとしており、アナログ回路やデジタル回路とは異なる独特の技術進化を遂げた。

電子機器の進化

アナログ 電子機器 LPレコード→Compact Disc NTSC TV → HDTV (Digital TV) フィルムカメラ→デジタルカメラ VHSビデオ → DVD アナログ携帯電話→デジタル携帯電話

デジタル 電子機器

#### ADCの基本機能

ADCは定まった時刻 $t_0$ における入力信号を(標本化)し参照信号を基準とする2進整数値に変換する(量子化)デバイス。

① 標本化 (サンプリング)

② 量子化

決まったタイミングで入力信号を抜き取る

分解能に応じた2進整数値に変換する

A. Matsuzawa

A/D変換原理を簡潔に表した 逐次比較型(SAR)ADC

$V_{in}(t_0) = V_{REF} \left\{ \frac{b_1}{2^1} + \frac{b_2}{2^2} + \dots + \frac{b_N}{2^N} \right\}$

2020.12.11

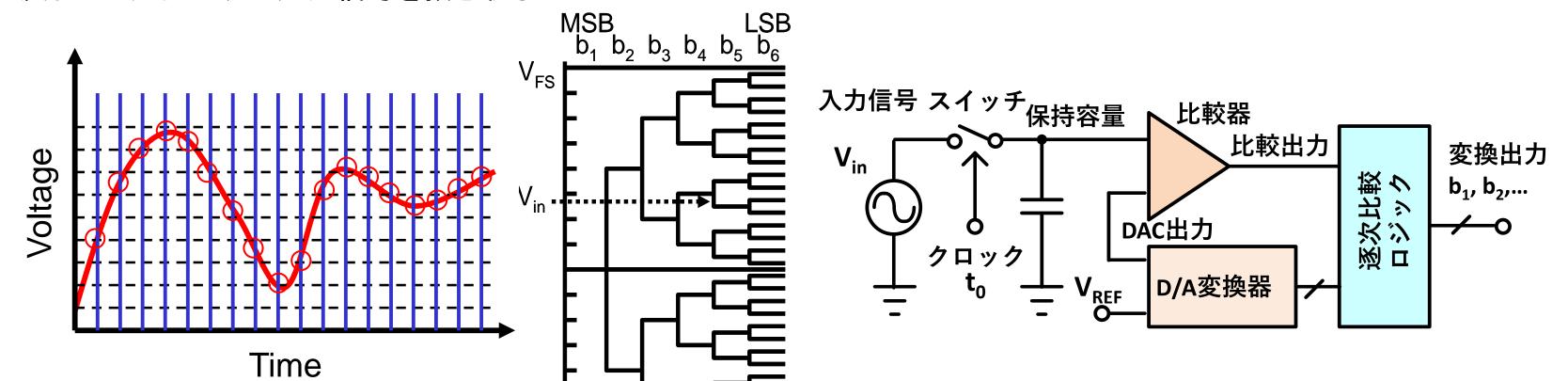

# ADCの変換周波数・分解能・用途

#### 用途に応じて変換周波数と分解能が異なる。これら2つはトレードオフの関係がある

2020.12.11 A. Matsuzawa

#### ADC の変換方式

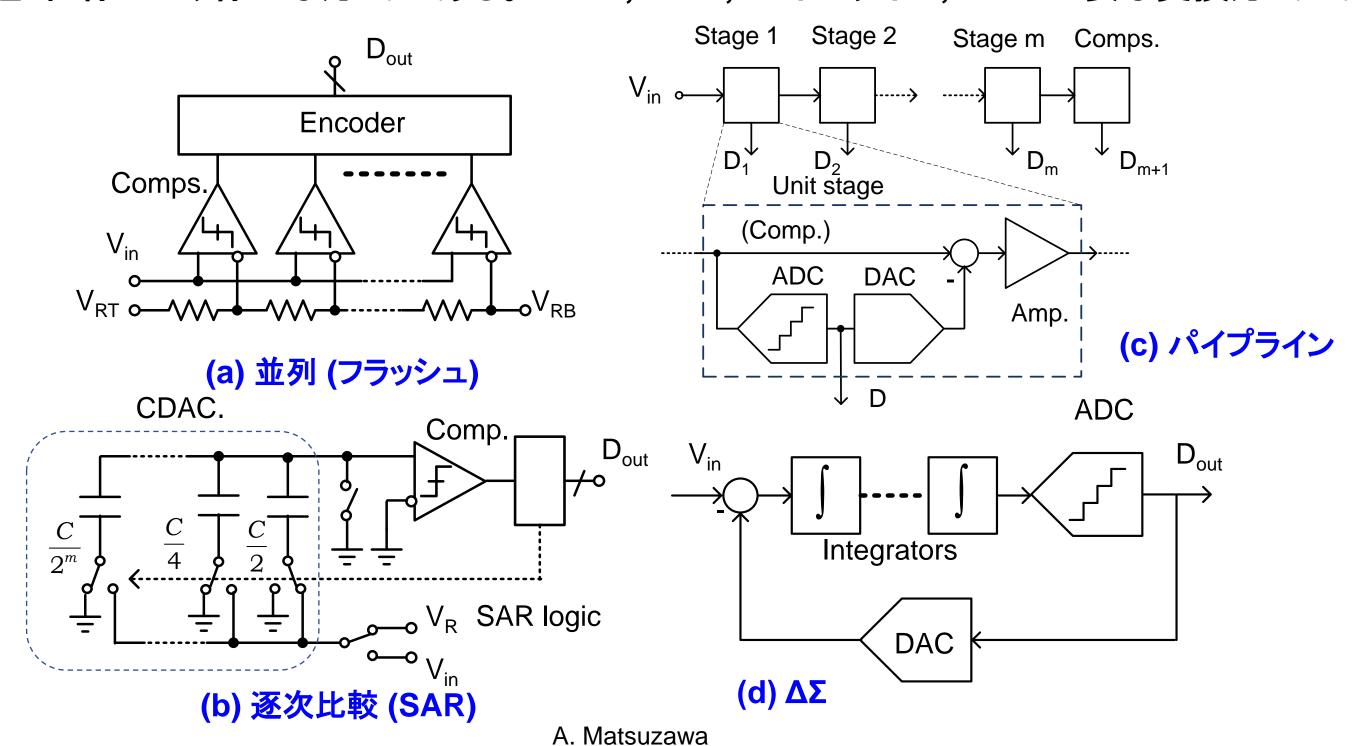

ADCは用途・仕様により様々な方式がある。Flash, SAR, パイプライン, ΔΣが主要な変換方式である。

2020.12.11

#### ADCに用いられる技術

ADC開発にはアナログとデジタルの両方の技術が必要

アナログ技術

高精度

広帯域

低ノイズ、低歪

高ダイナミックレンジ

低電力,低電圧

ダイナック動作

低ジッタ

デジタル技術

DS 変調

ランダム化

フィルタリング

キャリブレーション

補償

訂正

統計処理

A/D変換器

#### バイポーラADC

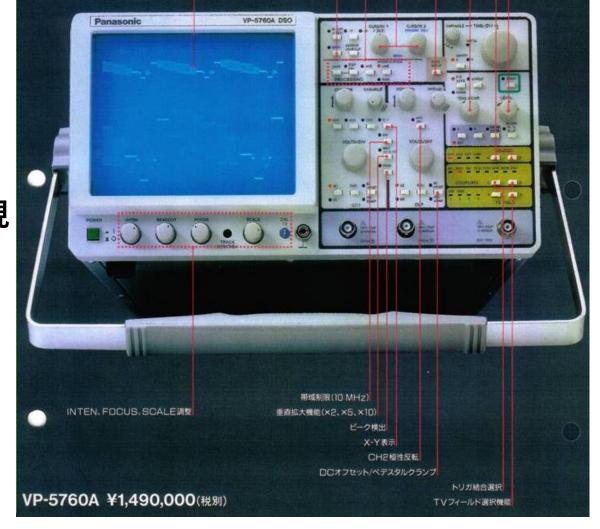

1970年代の終わりから始まったHDTV開発にはビデオ用ADCが必要だったが 当時はIC化された10ビットビデオ用ADCや、HDTVカメラ信号を変換可能なADC は存在しなかった。IC化されたHDTV用のADCはバイポーラ技術が用いられた。 この開発は初期のHDTV開発には貢献したが、市場が立ち上がらなかったので 実際には電子計測器・デジタルオシロなどに使用された。

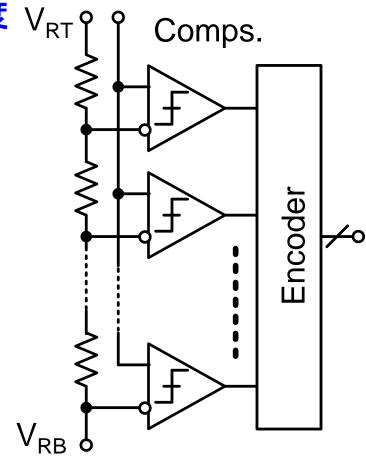

1970年代後半から1980年代におけるアナログ回路に使用できるデバイスはほとんどバイポーラであり、MOSは性能が悪すぎて使用できなかった。ただしバイポーラはADCに不可欠なスイッチと容量が使えなかったため並列型(Flash)に限定された

#### デジタルビデオ技術の開発開始

1978年に松下電器に入社し、1979年に中央研究所に配属された。 1978年に松下電器は総力を結集し6時間録画のVHSビデオの開発に成功。 以後ビデオ関連の売り上げは1兆円規模に達し、大黒柱に成長。

ビデオ機器はアナログ技術の集大成と言うべきものであったが、 次のデジタルTV・ビデオの開発に向けての研究が開始された。

1979年 中央研究所の配属同期と

Panasonic VHS Video NV-6000, 1979

#### MUSE: 初期の HDTV方式

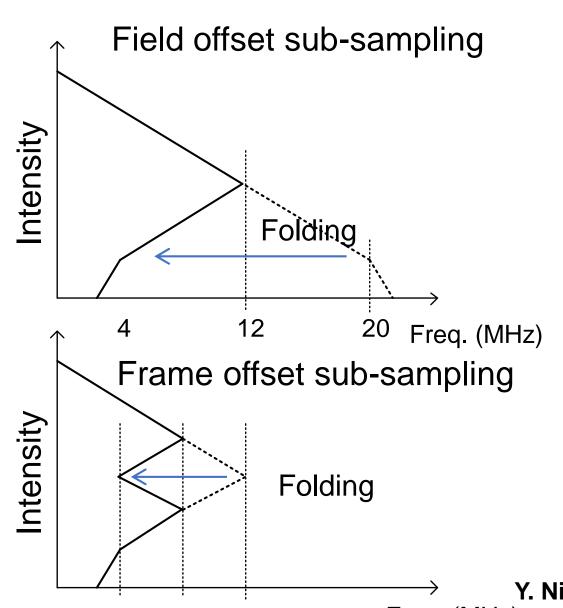

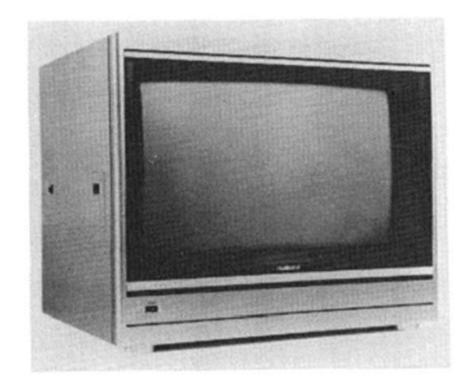

HDTV (デジタルTV) はNHKを中心に1970年代後半から開発が始まった。 初期のHDTVはMUSEと呼ばれるサブサンプリングによる帯域圧縮技術が用いられた。 このためにはTV信号をデジタル値に変換するADCが必要であった。

#### HDTV 方式は1990年代にMPEGベースに変更された

MUSE 受像機

MUSE 受像機用ボード (1989)

**MUSE: Multiple Sub-Nyquist Sampling Encoding**

Y. Ninomiya, et al., "An HDTV Broadcasting System Utilizing a Bandwidth Compression Freq. (MHz)Technique—MUSE," IEEE Transaction on Broadcasting, vol. BC-33, no. 4, pp. 130-160, Dec. 1987.

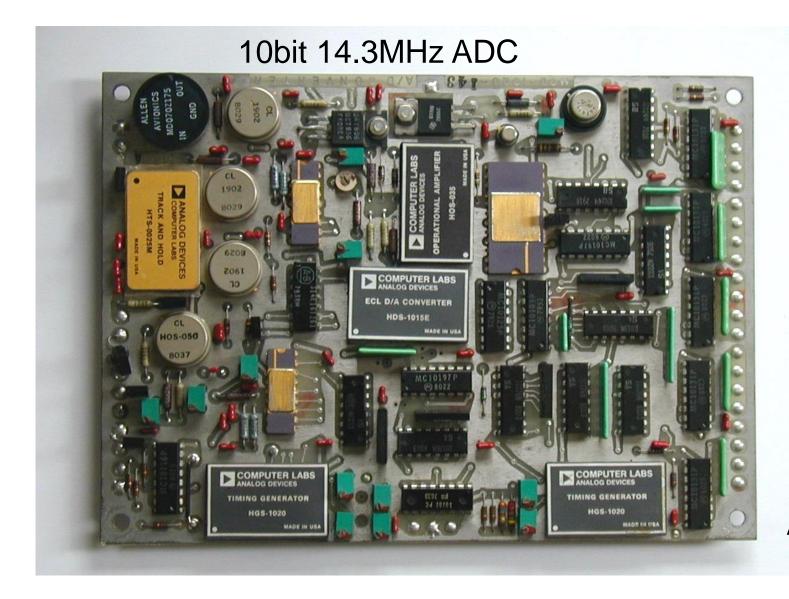

#### 1979年当時のビデオ用ADC

TV・ビデオのデジタル化の大きな課題はA/D変換器であった。 当時のビデオ用10bit A/D変換器はボードであり、集積回路化されていなかった。 非常に高価で、消費電力が大きく、民生品はおろか業務用にも使用できなかった。 各種デジタルTV・ビデオ機器を実現のためにIC化されたADCの開発が開始された。

1979年当時

100万円!! 20W

殆どのICがハイブリッドICである。 残りはTTL, ECLなどのロジックIC

Analog Devices Inc.

### 世界初のビデオ用10bit ADCの開発

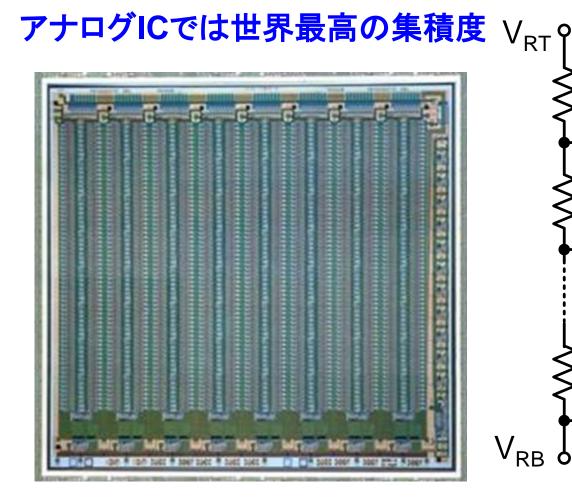

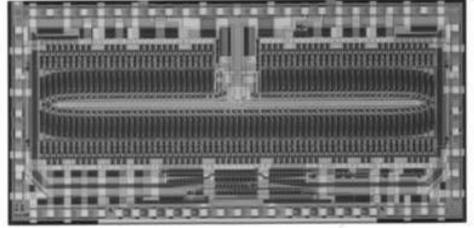

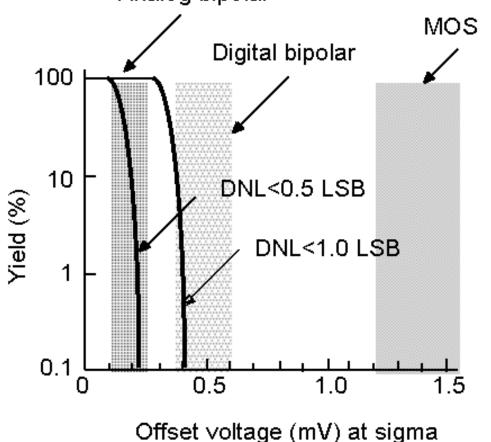

1982 に世界初の集積化されたビデオ用10ビットADCを開発。当時VHS用に高精度バイポーラ技術が開発されており、これを使用して低ミスマッチの比較器を実現。 世界最高の集積度を高精度で実現するため初めてステッパー露光を使用。

1023個の比較器 ミスマッチ電圧は0.2mV程度

世界初のデジタルビデオスイッチャー NTT 256QAM無線伝送 ソウル五輪のハイビジョン中継などに使用

Bipolar (3µm) 10b, 20MS/s, 2W \$ 800

10b 20 MS/s ADC

T. Takemoto, M. Inoue, H. Sadamatsu, A. Matsuzawa, and K. Tsuji, "A Fully Parallel 10-Bit A/D Converter with Video Speed," IEEE Journal of Solid-State Circuits, vol. SC-17, no. 6, pp. 1133-1138, 1982.

#### バイポーラ回路技術

バイポーラADCはサンプル・ホールドが使用できなかったのでサンプリング動作はラッチ回路で代用された。ADC方式はフラッシュに限られた。

この当時はTV・ビデオ用に高精度アナログ回路に適したバイポーラICが大量に生産された。 ロジックLSIもCMOSではなくNMOSが用いられた。

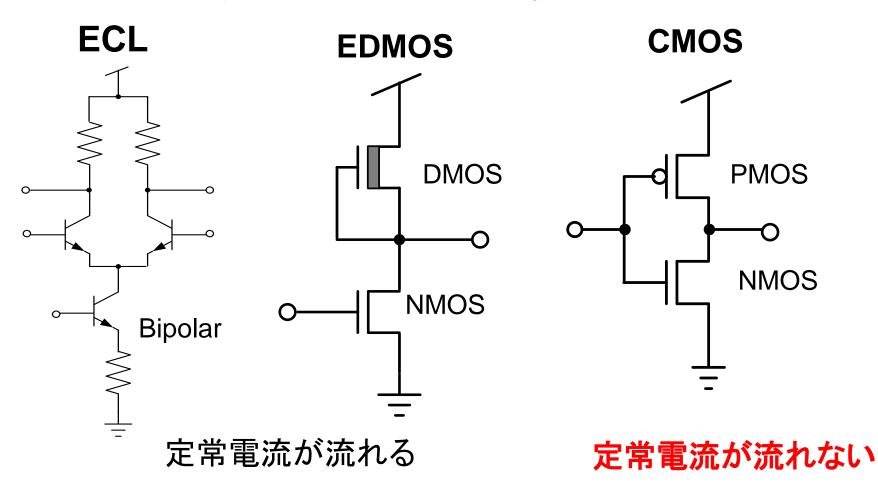

メインフレーム用超高速ロジックLSIはバイポーラを用いたECL回路が用いられた。

# $\neg$ $D_{out}$ CLK **CLKB** $V_{b1}$ 開発した比較器

当時の回路は全て定常電流が流れ、消費電力が大きかった

A. Matsuzawa

#### 開発したバイポーラADCとデジタルオシロでの使用

8b, 120MS/s, (1984)

HDTVカメラを実現 デジタルオシロを実現 バイポーラADCは超高速動作が可能なので、超高速ADCが必要なデジタルオシロに使用された

Panasonic:10b 100MHz Digital OSC (1986年)

M. Inoue, A. Matsuzawa et.al, "A Monolithic 8-bit A/D Converter with 120MHz Conversion Rate," IEEE JSC, 1984.

6b, 1GS/s, (1991) デジタルオシロに搭載

A. Matsuzawa, et. Al., "A 6b 1GHz Dual-Parallel A/D Converter," 1991 IEEE ISSCC.

#### いずれのADCも当時世界最高速

L0b 300MS/s (1993) HDTV信号の光送受信機を実現

H. Kimura, A. Matsuzawa, et. al., "A 10-b 300-MHz Interpolated-Parallel A/D Converter," IEEE JSC. 1993.

信号線とクロック線の遅延時間を合わせるための陸上トラックや鉄道模型のようなユニークなレイアウトは美しい工業デザインに選定されニューヨークのメトロポリタン美術館に展示された

#### **Bi-CMOS ADC**

1980年代の後半にはバイポーラとCMOSを集積したBi-CMOS技術が開発された。

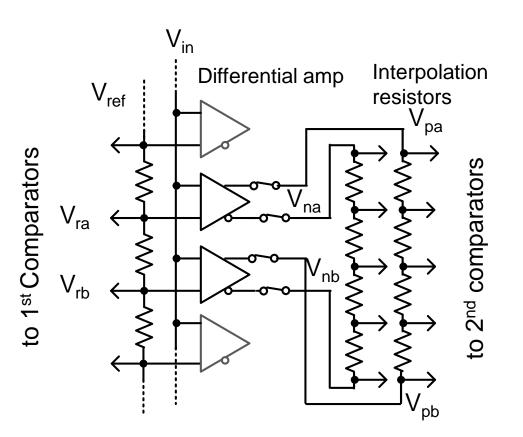

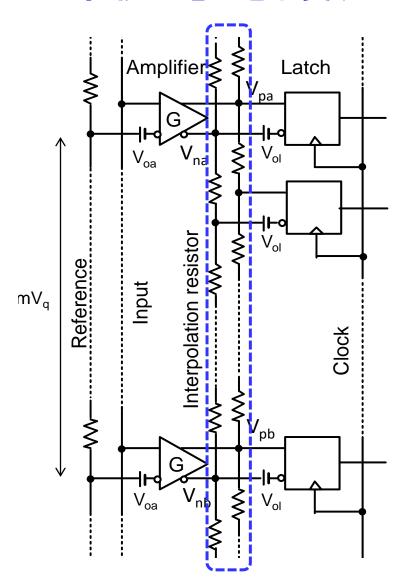

CMOSによりサンプルホールドが使用できるようになったので、2回の変換を行う2ステップフラッシュADCアーキテクチャを採用できたことにより、消費電力を下げることができた。しかし、2つの変換領域のつなぎが難しく、精度劣化を引き起した。このため滑らかなつなぎを実現する補間技術を開発した。

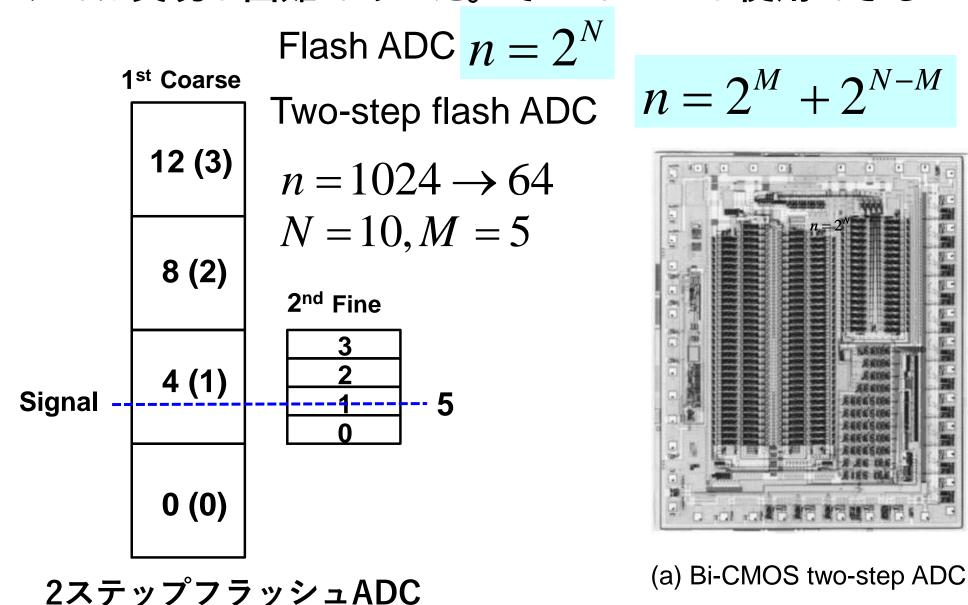

#### Bi-CMOS 2ステップフラッシュADC

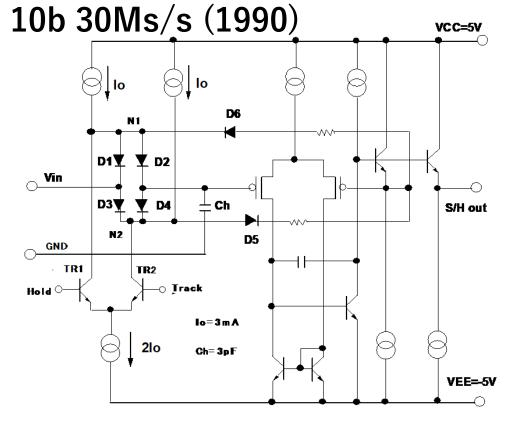

A/D変換を2回に分けることで,比較器を1/16程度にできるので,大幅な電力とコストの削減が可 能である。しかし信号を保持するサンプル・ホールド回路が必要でベース電流が流れるバイポー ラでは実現が困難であった。そこでMOSが使用できるBi-CMOS技術によるADC開発を行った。

(a) Bi-CMOS two-step ADC

n: # of comparators

N: Resolution of ADC

M: Resolution of the upper bit

(b) Bi-CMOS S/H

A. Matsuzawa, et. Al., "A 10b 30MHz Two-Step Parallel Bi-CMOS ADC with Internal S/H," 1990 EEE ISSCC.

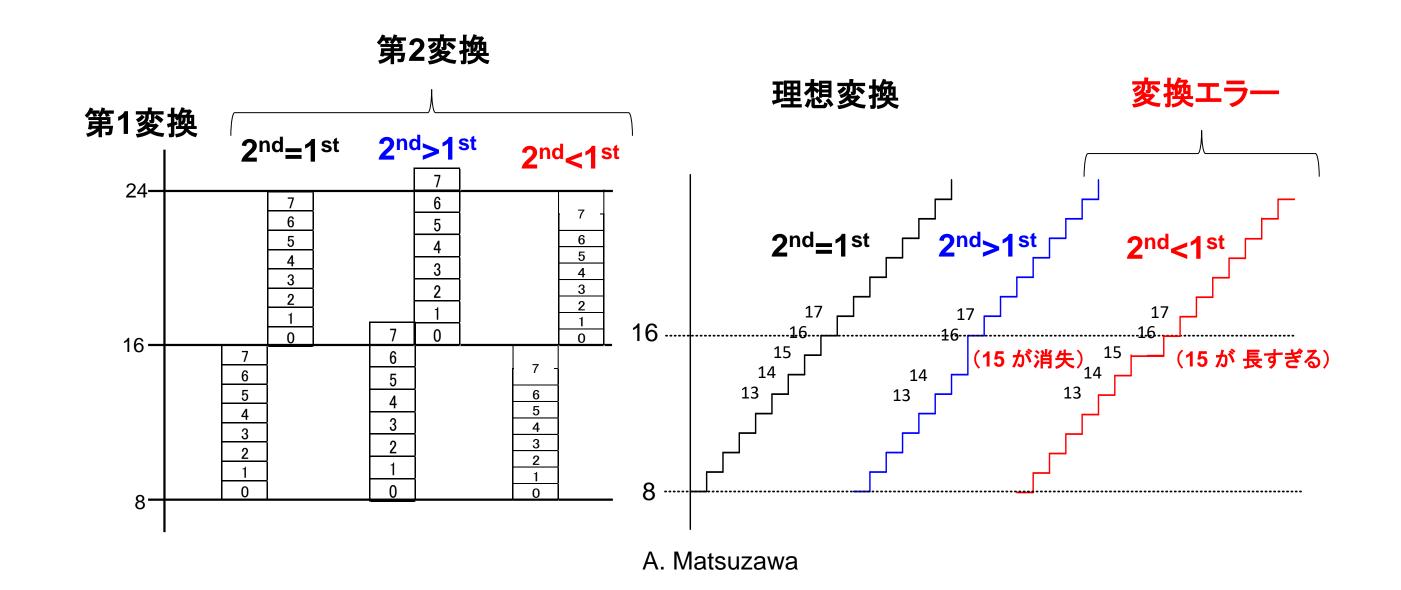

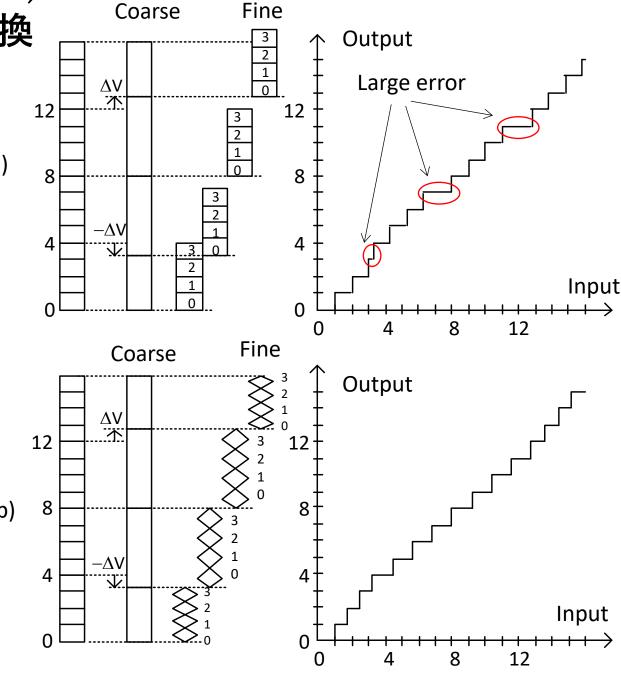

### 2ステップフラッシュADCの課題

2ステップフラッシュADC の大きな課題は、第2変換の参照電圧が第1変換の単位参照電圧と 1/4LMB (0.2mV 10bit)以下で合致しなければならないことで、ミスマッチにより変換エラーが生じる。 スイッチのフィードスルーやトランジスタミスマッチが大きな課題となる。

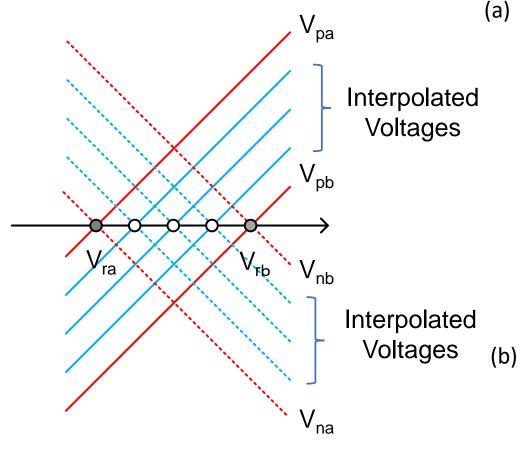

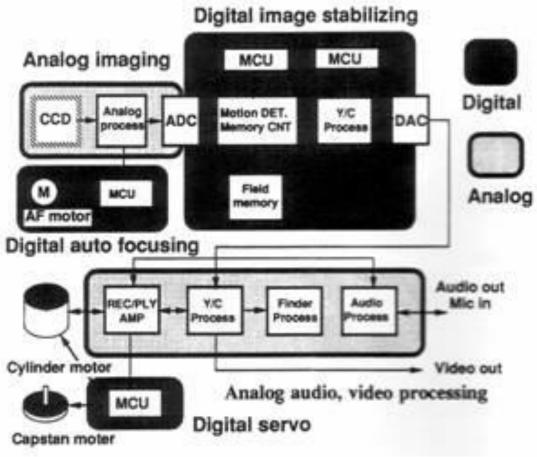

### 2ステップフラッシュADC用補間技術の開発

マッチング課題に対処するため「補間技術」を考案。 補間により第2変換(fine変換)の電圧範囲は第1変換(Coarse) の電圧に応じてバネのように適応的に伸縮するので大きな変換 誤差は発生しない。

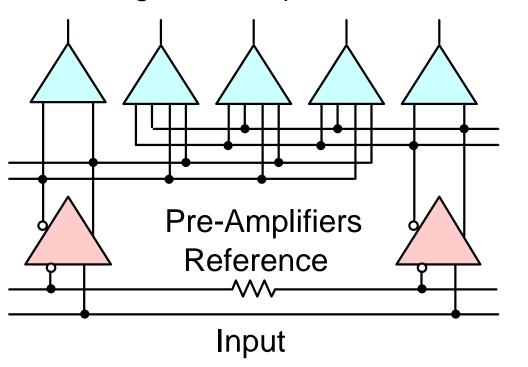

補間を用いた2ステップフラッシュ ADCの構成

補間による電圧生成

#### ミスマッチ誤差 (a) 通常方式 (b)補間を用いた時

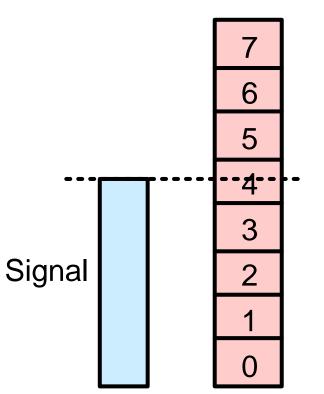

#### 補間の数学的表現

補間技術はその後のADCにも回路を変えて使用された。博士論文をまとめているときに、補間は数学的には内分法を表していることに気が付いた。信号に重みを掛けて加算できれば、どんな回路を用いても補間できる。

参照電圧を持たずに、2つの信号を重みを付けて加算することで A/D変換を行うというのは、それまでなかった技術

Scale (Reference)

通常のA/D変換 信号と参照電圧を比較する

内分法

補間によるA/D変換 信号に重みを付けて加算

$$x = \frac{(m-k)a + kb}{m}$$

#### 様々な方法で補間が実現できる

・抵抗補間:抵抗を用いたもの

・容量補間:容量を用いたもの

ゲート補間:リニア領域の抵抗を用いたもの

・時間補間:遅延時間を用いたもの

#### **CMOS ADC**

高集積化、アナログ・デジタル混載など、将来の発展のためにはCMOSを用いたADCの実現が不可欠であった。しかし、1990年当時、CMOSは精度が極めて悪く、しかも消費電力も大きかった。このためADCへの適用は困難と考えられた。

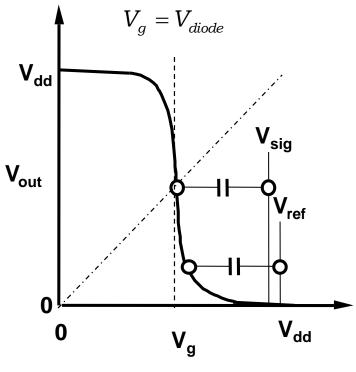

大きなブレークスルーは容量、スイッチ、インバータという、バイポーラでは実現困難な、CMOSの特徴を生かした回路技術であるチョッパ型比較器と、インバータ間の結合容量を用いることで容量補間回路を実現するとともにインバータ数を削減して、当時のビデオ用10bit ADCの消費電力を1/8に低減することに成功したことである。その後、ADCは100% CMOSに切り替わった。

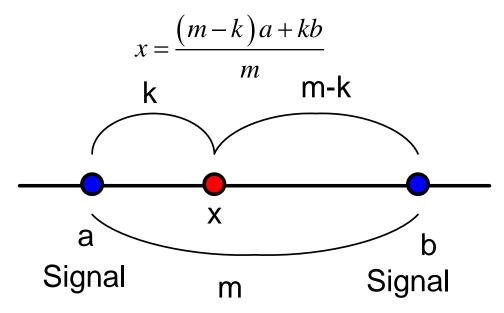

### デジタルハンディーカムコーダ

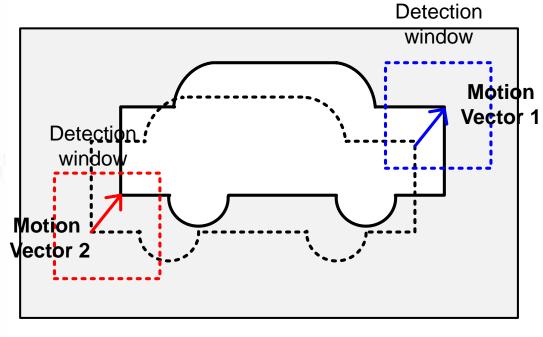

磁気テープに動画をアナログ記録するハンディーカムコーダはデジカメよりも先に開発された。 1990年前後、それまでのアナログ信号処理をデジタル信号処理に進化させ、手振れ補正を行うデジタルハンディーカムが開発された。画像用ADCが必要であるが、携帯機器のため、一層の低電力が求められた。またロジックと集積し低コスト化するためCMOS化が強く求められた。

デジタルハンディーカムコーダ

ブロックダイヤグラム

動きベクトルの検出

# バイポーラとCMOSの消費電力と精度

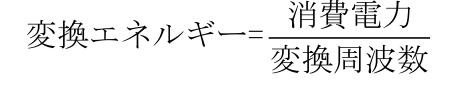

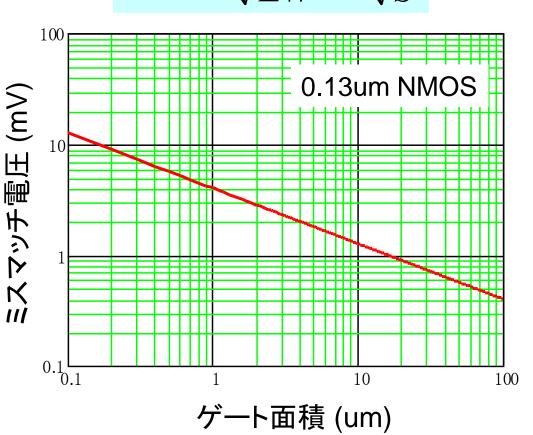

1990年当時, ビデオ用10bit ADCの消費電力は300mW程度と大きく, またバイポーラとCMOSの消費 電力はほぼ同等だった。MOSのミスマッチは10倍程度大きく, 低減には面積が増加し, 電力も増加した。

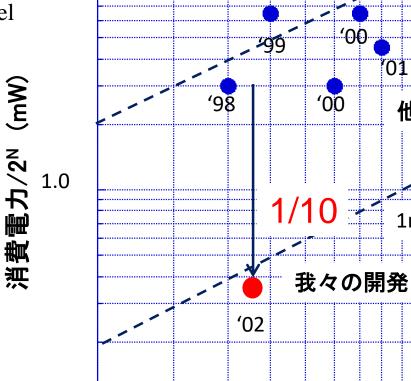

#### ビデオ用10bit ADCの変換エネルギー

MOSのミスマッチ電圧を下げるには ゲート面積の増大が必要である

# Bipolar CMOS Energy (nJ) 1/8 Our developed

**Published year**

#### CMOS チョッパ型比較器

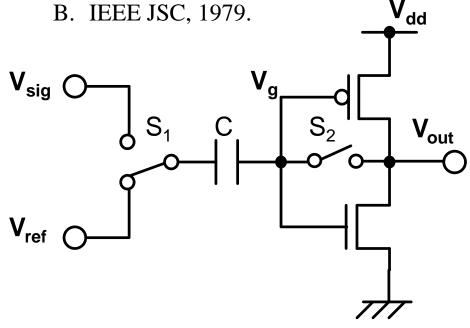

CMOS比較器は当初、バイポーラ比較器をMOSに置換えたものだったが、ミスマッチが大きいため精度が6ビット程度と低く、消費電力も大きかった。チョッパ型比較器はインバータ、容量、スイッチという最も単純な回路を組み合わせることで、ミスマッチ電圧を容量に吸収して精度を上げるだけでなく、比較、増幅、標本化、ラッチ動作というADCに必要な機能を実現することができる。定常電流も少なく、高精度・低電力ADCが可能である。

#### A. Yukawa, "A CMOS 8-Bit High-Speed A/D Converter IC," IEEE JSC. 1985.

#### 時分割で動作する離散時間型回路

AV<sub>DD</sub> AV<sub>DD</sub> Q<sub>I</sub> Q<sub>I</sub> Q<sub>I</sub> AV<sub>SS</sub> 基準抵抗 AV<sub>SS</sub> 入力信号 Vi クロック

A. G. F. Dingwall, "Monolithic Expandable 6 Bit 20MHz CMOS/SOS A/D Converter,"

(a) Chopper inverter comparator

(b) I/O characteristics

#### 超低電力ビデオ用10b CMOS ADCの開発

1993年、他のADCに対して変換エネルギーを1/8に下げたビデオ用10b CMOS ADCを開発。 チョッパ型比較器の結合容量をネスト状にすることで容量を用いた補間を実現。バネのように ミスマッチを吸収し、精度を8ビットから10ビットに向上させるとともに、不要となったイン バータを除去して電力を削減した。以後、ほとんどのADCがCMOSを用いるようになった。

K. Kusumoto, A. Matsuzawa, et al., "A 10-b 20-MHz 30mW Pipelined Interpolating CMOS ADC," IEEE JSC. 1993.

容量補間を用いた10b 20MS/s CMOS ADC (1993)

A. Matsuzawa

Published year

28

#### 初期のアナログ・デジタル混載LSI

低電力CMOS ADCの開発に成功したことで、デジタルフィルターや、マイコンなどのデジタル 回路との混載が可能となり、ポータブルAV機器の小型化、低コスト化、デジタル化に大きく貢献 した。

初期のアナ・デジ混載LSI

**Digital Video filter**

8b CPU

Low speed ADC;DAC

**Video ADC**

A. Matsuzawa, "Low-Voltage and Low-Power Circuit Design for mixed Analog/Digital Systems in Portable Equipment," IEEE Journal of Solid-State Circuits, Vol.29, No.4, pp.470-480, 1994.

#### ローパワーエレクトロニクス

ローパワー技術はデジタル<mark>携帯機器の実現</mark>には不可欠なため日本の民生機器メーカーが主導した。例えば、電卓、時計、デジタルハンディーカム、デジカメ、デジタル携帯電話などである。その後、ウエアラブル機器やインプランタブル機器などの新規分野の開拓に貢献している。スマートフォンの登場にとってもローパワー技術の発展が欠かせない。

一方,高性能コンピュータの開発に対してもローパワー技術が重要である。メインフレームにおいてはバイポーラを用いたECLなどの高速回路が用いられたが、消費電力の限界に直面し、低速だがローパワーなCMOSにとって代わられた。消費電力が大きい回路は集積密度向上が困難で演算性能を上げられないうえに、実装コストが高くつく。CPUも2004年辺りに電力限界を迎え、クロック周波数を上げずに並列度を上げることで演算性能を上げるマルチコアに転換した。現在、AI用チップの消費電力が大問題になっている。歴史を振り返ると技術はいつも低消費電力技術を選択している。

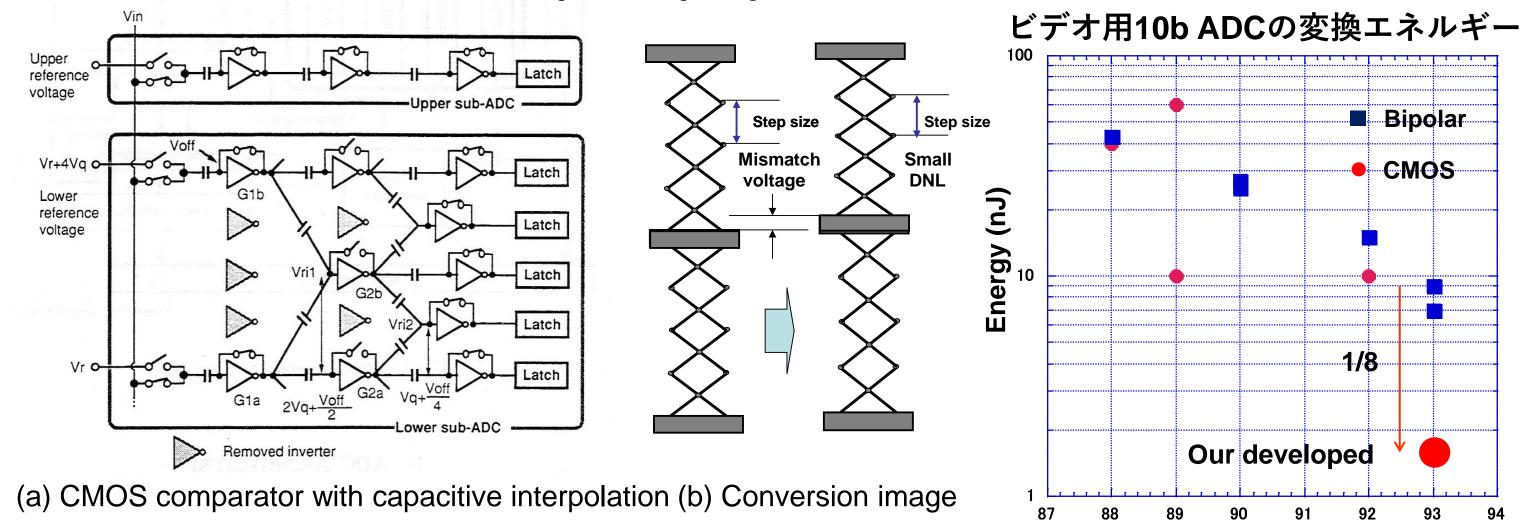

#### ローパワーエレクトロニクスの振興

1993年の画期的な超低電力CMOS ADCの開発により、1994年のVLSIシンポでのローパワー技術に関する招待講演やJSCへの招待論文がきっかけとなって、ローパワー技術に関する関心が高まり1995年に世界初のローパワーエレクトロニクスに関する国際WSを開催した。 以後、ローパワー技術は集積回路技術の大きな潮流になって今日に続いている。

当時、米国ではローパワー技術に対する関心が低く、米国のローパワー技術の研究者は孤独を感じていた。米国ではメインフレームに代表される高速コンピュータが産業と学問の中心で、エネルギー消費に関する関心は低かった。日本は民生機器、携帯機器が産業の中心にありローパワー技術への関心は高く、しばらくの間開発をリードした。

日経BP社:日経マイクロデバイス編 1994年 [低電力LSIの技術白書 1ミリ・ワットへの挑 戦]

設計/ロジック/アーキテクチャ

検討した

Part. 2

1mW台に挑戦するアーキテクチャ 高速化から視点を切り替える

低電力アーキテクチャとは何か、今後のLSI市場でどのような役割を果たすのか、 を解説する。低電力アーキテクチャとは、所望の機能を達成しながら低電力化するアーキテクチャである。高スルーブット化技術と、無駄なスイッチングを減ら す技術が2本柱になる。こうした低電力アーキテクチャは、専用LSIに適用する 場合が多くなる。ネットワークの整備により、低電力で処理性能の高い専用LSI が普及しやすくなった。汎用LSIと補完しながら、マルチメディア時代を創る。

設計/ロジック/アーキテクチャ

松下電器産業 半導体研究センター **松澤 昭**  画像向けなどアーキテクチャを専用化 チップ面積を抑えつつ電力削減

専用回路と汎用回路の双方を搭載する専用プロセサは、チップ面積の増加 を種力抑えながら低電力化できる。このアーキテクチャ設計の考え方と手 法を分類し、系統的に解説する。さらに、ディジタル携帯電話向け音声処 理DSPや、MPEG2などの画像処理DSPに適用したアーキテクチャをケ ース・スタディとして挙げる。低電力化の際の狙いどころの絞り方や、チ ップ面積をほとんど増やさずにスルーブットを高める手法などを示す。 松下電器産業 半導体研究センター 松澤 昭 上田 勝彦 青野 邦年

アナログのみならずデジタルのローパワー化も

### 開発例:アダプティブ電源内蔵MTDSPの開発

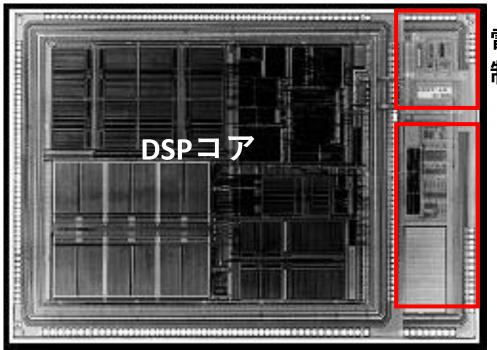

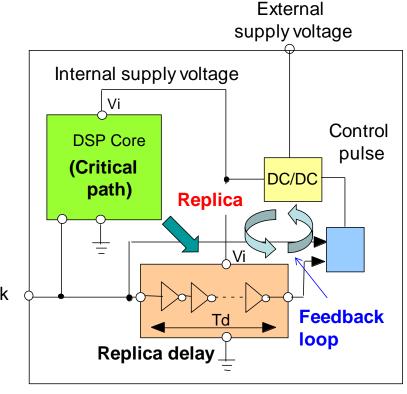

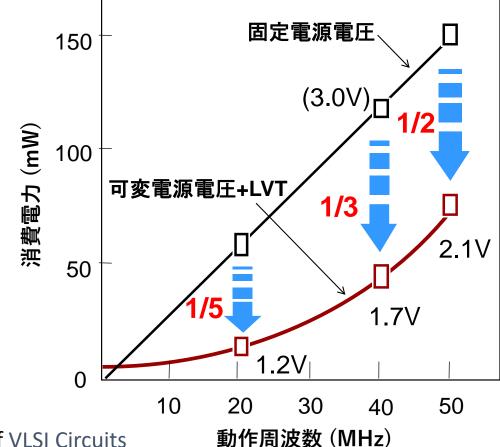

95年よりNTT様とMTCMOSなどのローパワー技術の共同開発を行った。動作状態を検知し、最小電力となるように内蔵したオンチップDC/DCの電源電圧を制御するMTCMOSを用いたDSPを開発し、これを用いて1998年の長野冬季オリンピックの会場連絡用腕時計型PHSを開発した。

#### 腕時計型携帯電話を開発

ローパワー技術により携帯機器、ウエアラブル機器、インプランタブル機

器などの新規デバイスが実現できる

#### アダプティブ電源内蔵MTDSP (1997)

電源電圧 制御回路

On chipclock DC/DC

S. Sakiyama, A. Matsuzawa, et al., 1997 IEEE Sym. Of VLSI Circuits

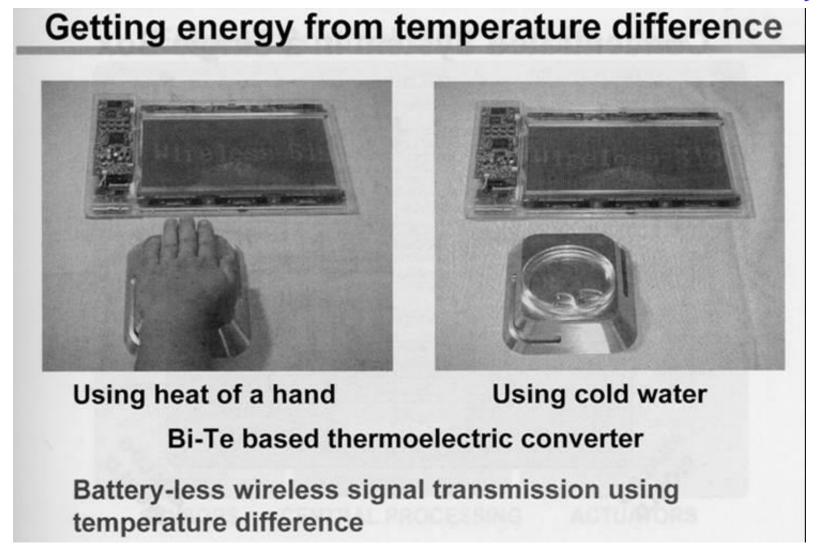

### 開発例:自然エネルギー動作無線PDA端末の開発

2000年から4年間のNTTを中心とする複数の企業・大学によるNEDOプロジェクト。 低電圧・低消費電力に優れたFDSOIを用いてマイコン・メモリ・アナログRF回路を開発し、体温などの 自然エネルギーで動作する無線PDA端末を開発した。松下は低電圧アナログRF回路開発を担当。

プロジェクト概要はSpringerから出版された

**Fully-Depleted SOI CMOS**

**Circuits and Technology**

for Ultralow-Power Applications

Douseki, et al., 2003 IEEE ISSCC,

-1.7mW/ 0.7Vを発電

#### アナ・デジ混載システムLSI

微細化の進展とともに、システム全体をワンチップに集積できる時代が到来した。 しかしながら、ボトルネックはいつもADCの搭載で、特に搭載可能な低消費電力動作が 求められた。

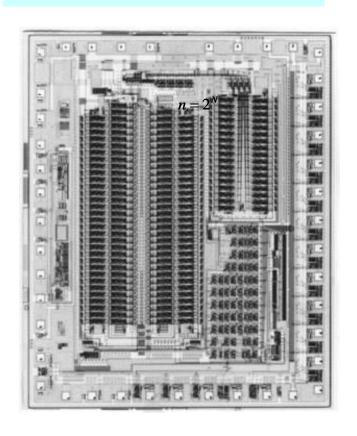

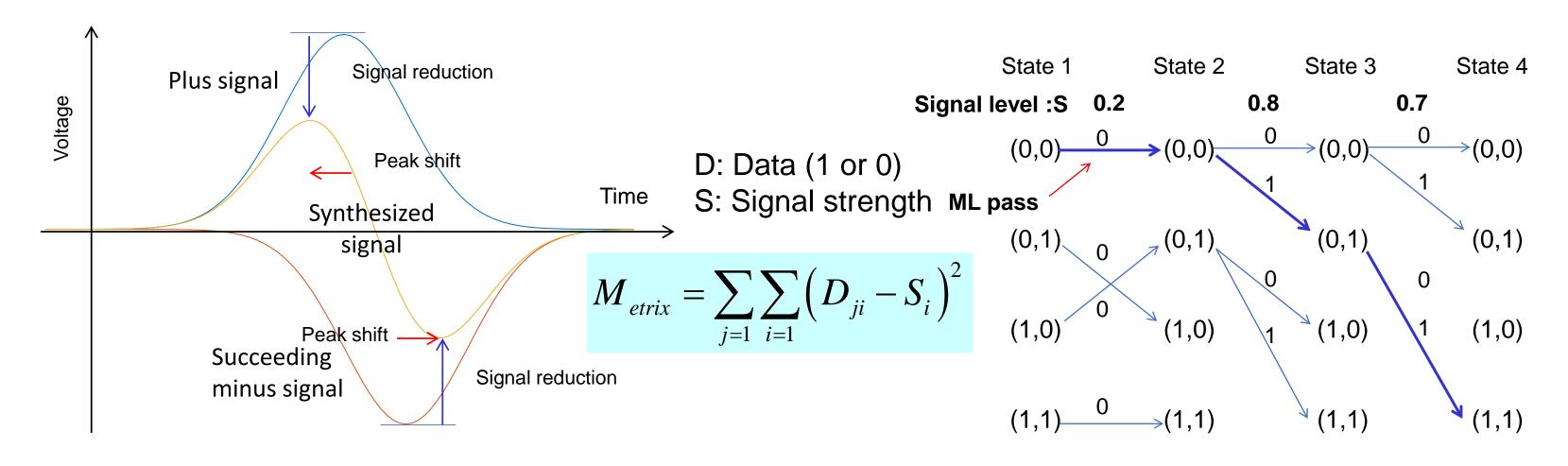

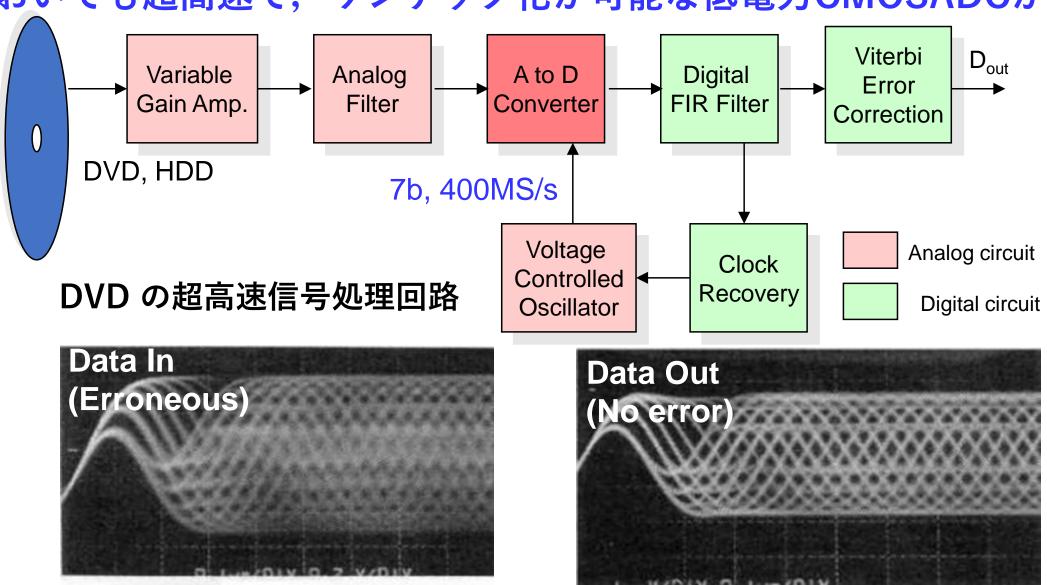

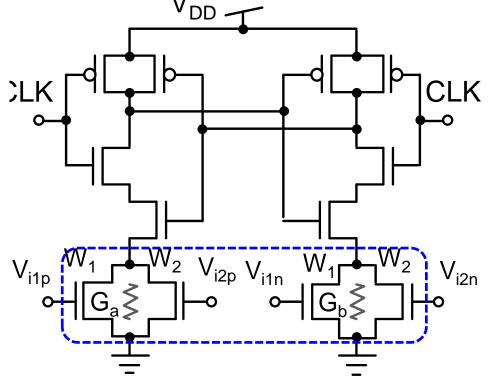

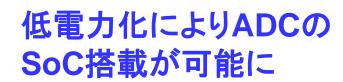

HDDやDVDなどの記録システムでは記録密度の向上に伴い、信号間干渉(ISI)が深刻化し、この解決のためにはピックアップ信号をA/D変換し、波形等価や誤り訂正を行うデジタル信号処理技術が用いられるようになった。このためADCの変換周波数は数100MHzと高く、消費電力も大きいためそのままではワンチップ搭載は困難であった。そこで、定常電流を消費しないダイナミック型比較器に電力消費増なしで高精度化のための補間が可能な重みづけゲート補間回路を導入し、当時の他のADCの約1/10の消費電力の50mWで動作する7bit、400Ms/sのADCを開発し、世界初のDVD用完全ワンチップアナ・デジ混載SoCを開発した。DVDの高性能化、低電力化、小型化、低コスト化に大きく貢献した。

### 記録システムの課題と解決策

HDDなどの記録システムは閾値処理により0,1判定を行っていたが、記録密度の上昇に伴う信号間干渉:ISIによる信号レベルの低下やピークシフトにより誤判定が多くなった。そこで対策としてピックアップ信号をADCで数値に変換し、仮想のデジタル値との差を求め、最も確率の高いビット列を選ぶことで誤り率を下げる技術が開発された。

磁気記録のおけるISI (Inter Symbol Interference)

Maxum-Likelihood method using Viterbi decoder

#### DVD システムの超高速信号処理

DVDシステムにおいても記録密度の向上とともにISIが生じ、誤りが多くなった。特にレーザで多値書込みを行うDVDレコーダにおいては顕著になったので、信号を7b, 400Ms/s程度のADCで変換後、波形等価や誤り訂正を行うようになった。

民生機器においても超高速で、ワンチップ化が可能な低電力CMOSADCが必要となった。

2025/3/27

### 超高速CMOS ADCの開発

#### 超高速ADCの民生機器応用にはCMOS化と低電力・低コスト化が不可欠

### 91年当時、世界最高速の6b ADC バイポーラ技術

6b, 1GHz ADC, 2W, 1.5µm Bipolar

A. Matsuzawa, et. al., "A 6b 1GHz Dual-Parallel A/D Converter," 1991 IEEE ISSCC.

#### 当時、世界最高速のCMOS ADC

K. Sushihara and A. Matsuzawa, ISSCC 2000.

6b, 800MHz ADC 400mW, 2mm<sup>2</sup> 0.25µmCMOS

他のADCに比べ1/10の消費電力

500

変換周波数(MHz)

10mW/Gsps

他の開発

1mW/Gsps

2000

1000

#### 高速性を維持し、電力を1/8に下げた

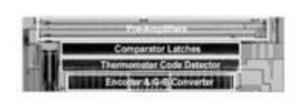

7b, 400MHz ADC 50mW, 0.3mm<sup>2</sup>, 0.18µmCMOS

Technology: 0.18um CMOS/3AL,1PS Area: : 0.88mm X 0.34mm K. Sushihara and A. Matsuzawa, "A 7b 450MSPS 50mW CMOS ADC in 0.3mm<sup>2</sup>," 2002 IEEE ISSCC.

0.1

200

10.0

# ゲートで重みを付けた補間

CMOS フリップフロップ (F/F) のソースにリニア領域で動作するMOS TRを挿入することでゲートの重みにより補間が実現できる。F/Fは貫通電流が流れず、補間に抵抗を用いないので、高速・低電力動作が可能。

#### 抵抗で電力を消費する

抵抗を用いた補間回路

$$G_{a} = rac{\mu C_{ox}}{L} \Big[ W_{1} \Big( V_{i1p} - V_{T} \Big) + W_{2} \Big( V_{i2p} - V_{T} \Big) \Big] \Big\}$$

$G_{b} = rac{\mu C_{ox}}{L} \Big[ W_{1} \Big( V_{i1n} - V_{T} \Big) + W_{2} \Big( V_{i2n} - V_{T} \Big) \Big] \Big]$

リニア領域の抵抗で補間が実現できる

ダイナミック回路:電力を消費しない

Gate-weighted interpolation

K. Sushihara and A. Matsuzawa, 2002 IEEE ISSCC.

$$G_{a} - G_{b} = \frac{\mu C_{ox}}{L} \left[ W_{1} \left( V_{i1p} - V_{i1n} \right) + W_{2} \left( V_{i2p} - V_{i2n} \right) \right]$$

$$W_{1} : W_{2} = \frac{m - k}{m} : \frac{k}{m} \quad k < m$$

Comparator latches with gate -weighted interpolation

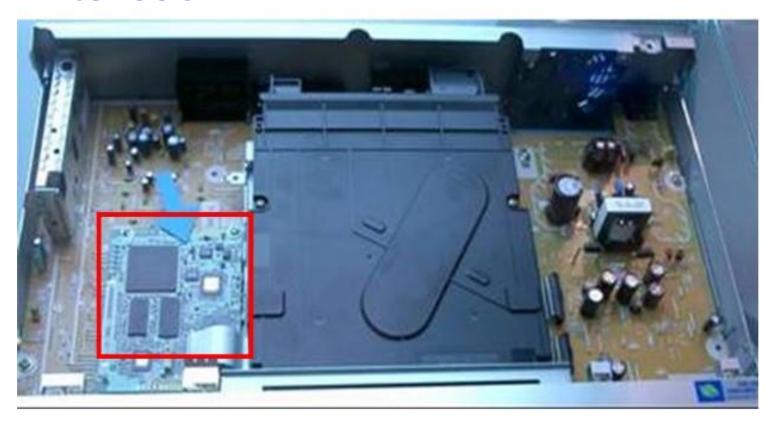

# DVD 用完全ワンチップアナ・デジ混載SoCの実現

#### DVDシステムを完全にワンチップ化した世界初のDVD用アナ・デジ混載SoC

#### その後SoCによるシステムレベルの集積が進展

Okamoto,..., A. Matsuzawa., ISSCC 2003, JSC 2003.

0.13µm, Cu 6Layer, 24MTr

SoC: System on a Chip (システムLSI)

7b, 400MS/s ADC —

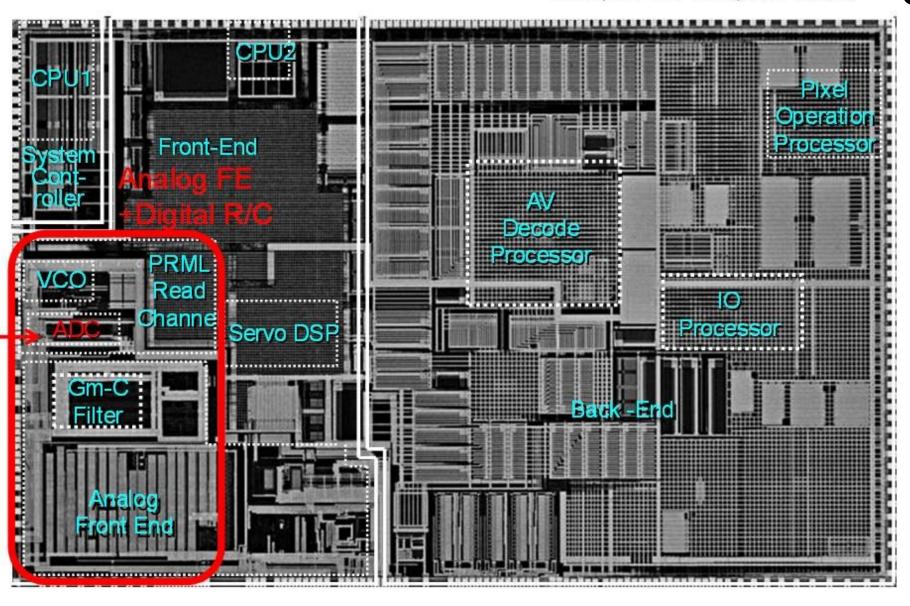

## ワンチップアナ・デジ混載SoCの威力

システム集積が可能なアナ・デジ混載SoCは、機器の高性能化、低電力化、簡素化、低コスト化に大いに貢献した。また、DVDのノートPC搭載を可能にした。

多くのチップが1つのSoCに集積され、残りはメモリとインターフェースチップだけになった

Before SoC '2000 Model

After SoC '2003 Model

### SAR ADCの革新

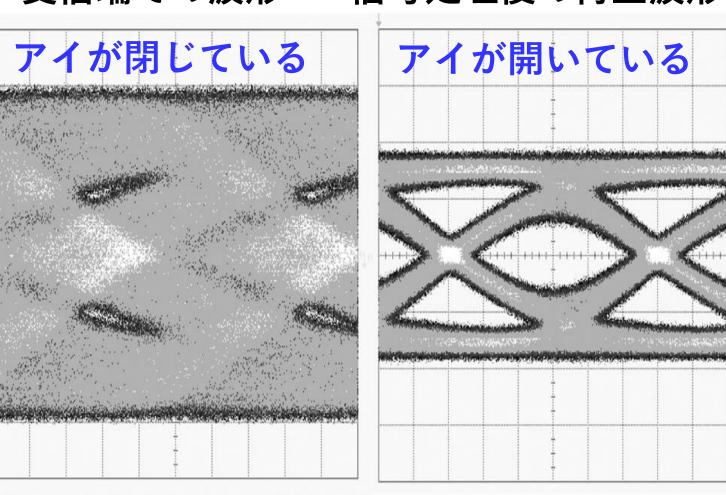

電気ケーブル通信では高周波化に伴う伝送ロスの増加、光通信においては誘電分散によりISIが深刻化し、デジタル記録システムと同様、受信信号をA/D変換後、波形等価や誤り訂正を行うデジタル信号処理が用いられるようになった。あいかわらずネックはADCで100GS/s程度の超高速動作が求められるほか、これに伴う消費電力増大も大きな課題となった。

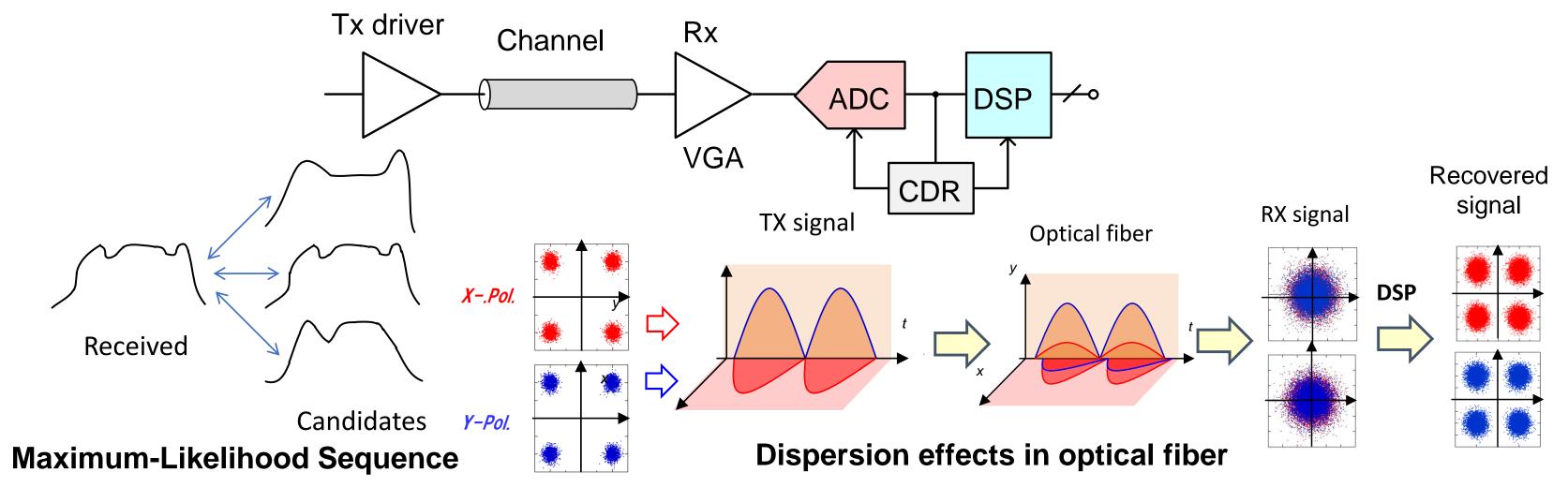

当初、SiGeなどの超高速デバイスを用いたフラッシュADCも検討されたが、変換周波数向上が困難で、かつ消費電力が極めて大きかった。現在はSAR ADCが用いられている。SAR (逐次比較)ADCは1970年代から使用されてきたアーキテクチャであるが、近年急速に性能を上げるとともにエネルギー消費を下げており、面積も小さいため現在の主流ADCとなっている。容量のみで構成され、定常電流を流さないダイナミック動作により究極の低エネルギー動作が可能である。デジタル回路と同様に微細化により小面積化、高速化、英エネルギ化が可能である。したがって並列化に向いており、個々のADCの変換周波数はそれほど高くはないが、全体として100GS/sを超える超高速動作が可能である。

2020.12.11 A. Matsuzawa

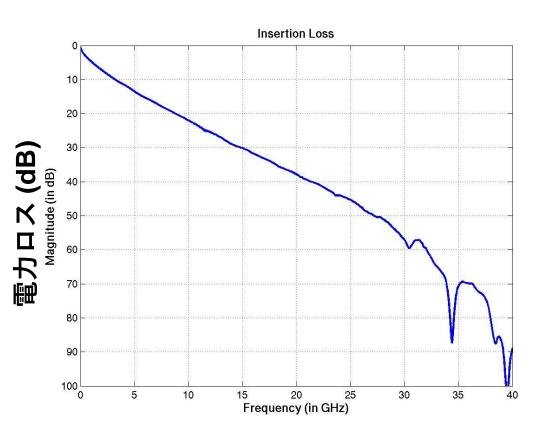

# 電気ケーブル伝送のISI課題

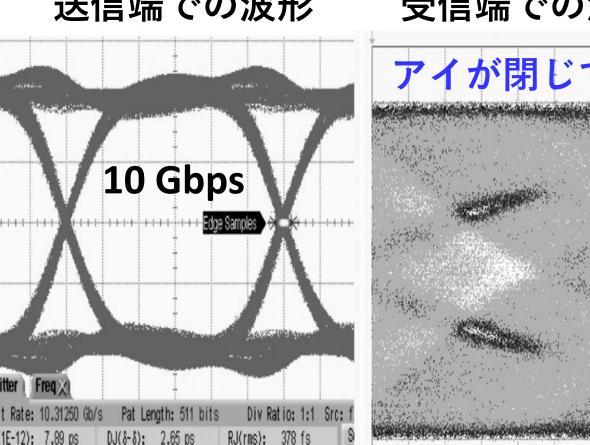

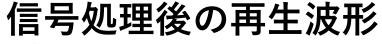

ケーブルの高域減衰により受信端ではアイが閉じるが、ADC後のデジタル信号処理 によりアイが開いた再生波形が得られる。

### 電気ケーブルロス

周波数 (GHz)

#### 送信端での波形

DDJ(p-p): 2.94 ps

受信端での波形

J. Cao et al., "A 500 mW ADC-based CMOS AFE with digital calibration for 10 Gb/s serial links over KR-backplane and multimode fiber," IEEE Journal of Solid-State Circuits, vol. 45, no. 6, pp. 1172-1185, June 2010.

A. Matsuzawa

# 電気ケーブル伝送と光ファイバー通信用信号処理

電気ケーブル伝送においては高周波化による伝送ロスの増加によりアイが開かなくなる。 また、光ファイバー通信においても誘電分散効果により偏波面間で位相シフトが発生し、信号再生 が困難になる。そこで、デジタル記録システムと同様にDSPで波形等価とML法などを用いた誤り 訂正を行う。このためには100GS/sレベルの超高速ADCが必要となる。

H-M, Bae et al., "An MLSE Receiver for Electric Dispersion Compensation of OC-192 Fiber Links," IEEE JSC, 2010.

. Miyamoto and M. Tomizawa, "High-Capacity Scalable Optical Communication for Future Optical Transport Network," 2014 IEEE ISSCC

# インターリーブSAR ADC

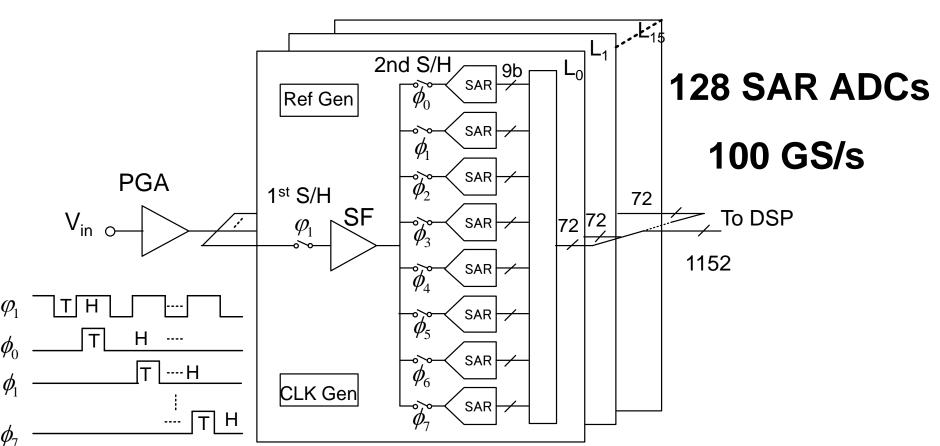

100GS/sレベルの光通信用ADCはインターリーブSARADCが使用されている。SAR ADCは小型, 低電力で低速であるが、128程度のインターリーブにすることで超高速動作を実現し、消費電力 や面積も適度な大きさに収まっている。超高速処理回路を実現するうえで低電力・低エネルギー 小面積であることは極めて重要である。 Ultra-high-speed interleaved SAR ADC

R. E. Suarez, P. R. Gray and D. A. Hodges, "All-MOS charge-redistribution analog-to-digital conversion techniques. II," 1975 IEEE JSC

. Cao, et al., "A Transmitter and Receiver for 100Gb/s Coherent Networks with Integrated  $4\times64$ GS/s 8b ADCs and DACs in 20nm CMOS," 2017 IEEE ISSCC.

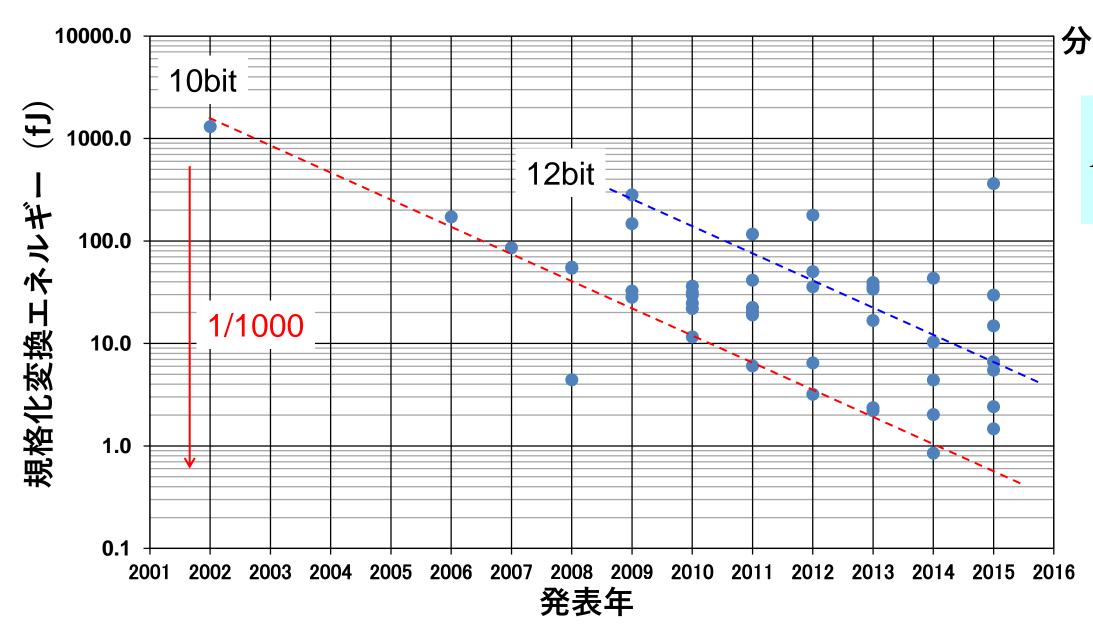

## SAR ADCの変換エネルギー低減の進歩

ADCは消費電力が大きく、機器開発のネックであったが、SAR ADCは2002年から約12年で消費エネルギーを1/1000に激減させた。

分解能で規格化した消費エネルギー

$$FoM_W = \frac{P_d}{f_s \times 2^{N'}}$$

N':有効ビッ

2020.12.11 A. Matsuzawa

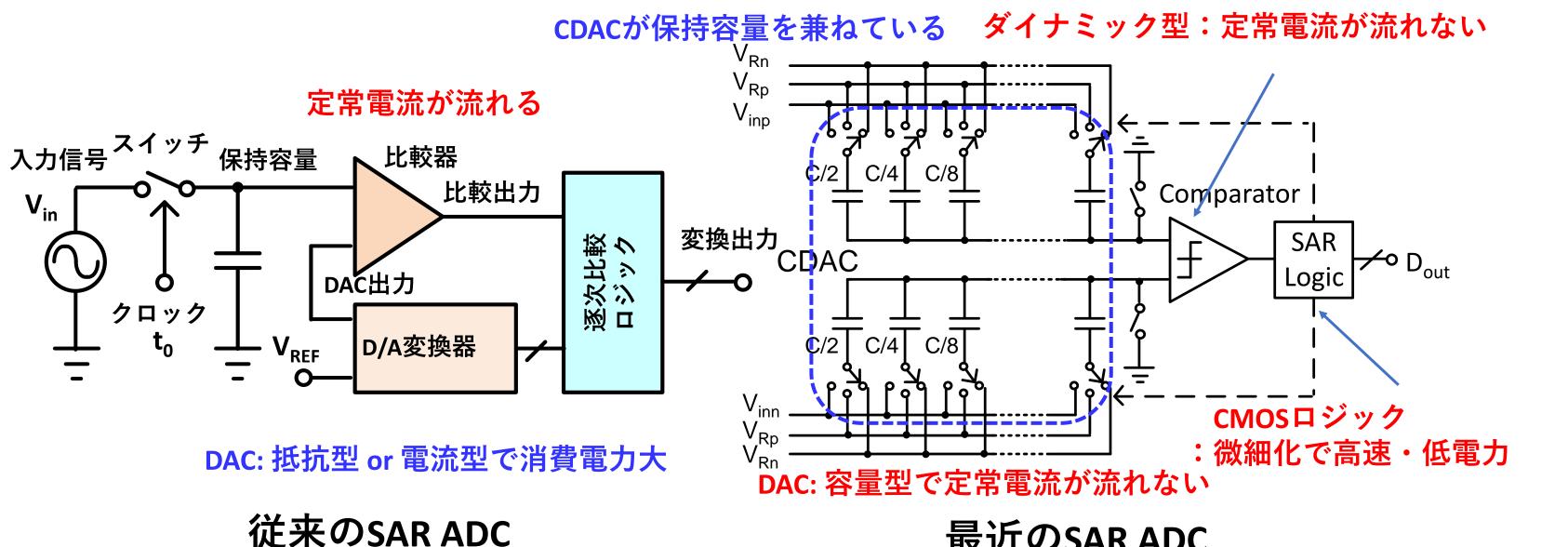

### SAR ADCの進化

従来のSAR ADCは定常電流が流れる比較器とDACを使用していたが、最近は定常電流が流れないダイナミック型比較器、保持容量を兼ねる容量DACを使用し、回路全体で超低電力動作が可能になった。更に回路全体として微細化により高速化、低エネルギー化が図れるようになった。

従来のSAR ADC

A. Matsuzawa

A. Matsuzawa

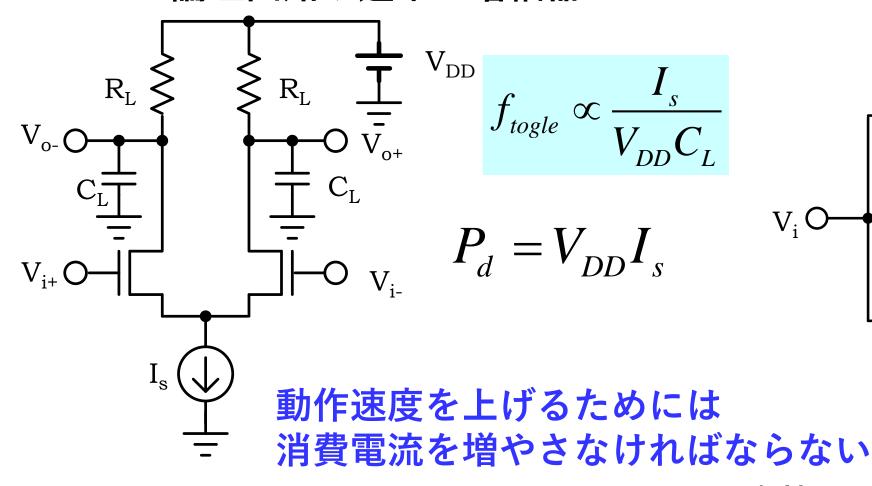

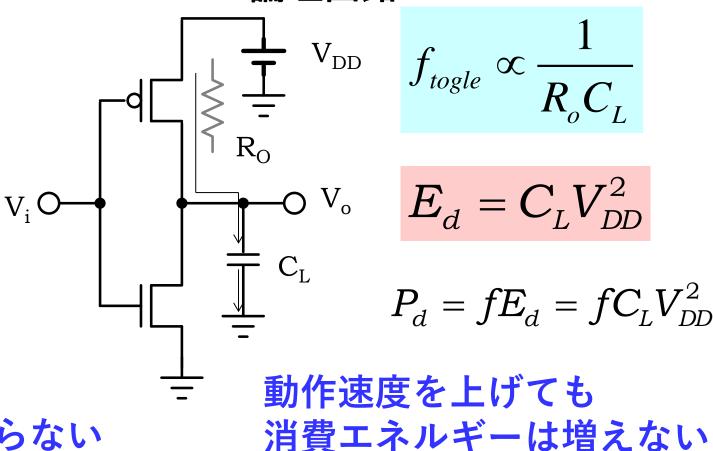

# 低エネルギーADC 設計の基本コンセプト

### CMOS論理回路のようなADCの構成が鍵

- ・貫通電流が流れず、殆どすべての電流が負荷容量の充放電に使用される

- ・論理状態確定後は電源電流は流れない

- ・オン抵抗を減らして高速化を図っても消費エネルギーは増加しない

- ・素子のスケーリングにより高速化, 低エネルギー化が図れる

#### CML 論理回路や通常の増幅器

#### CMOS 論理回路.

A. Matsuzawa

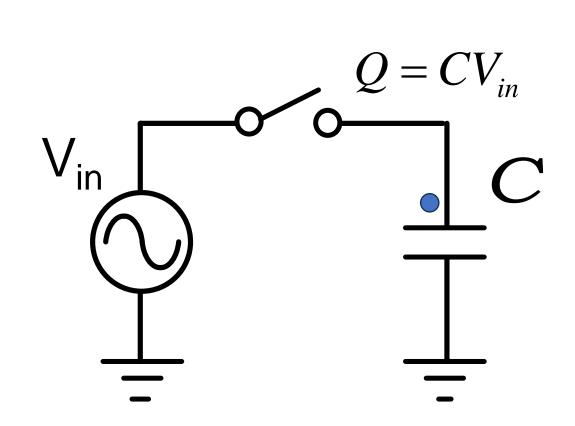

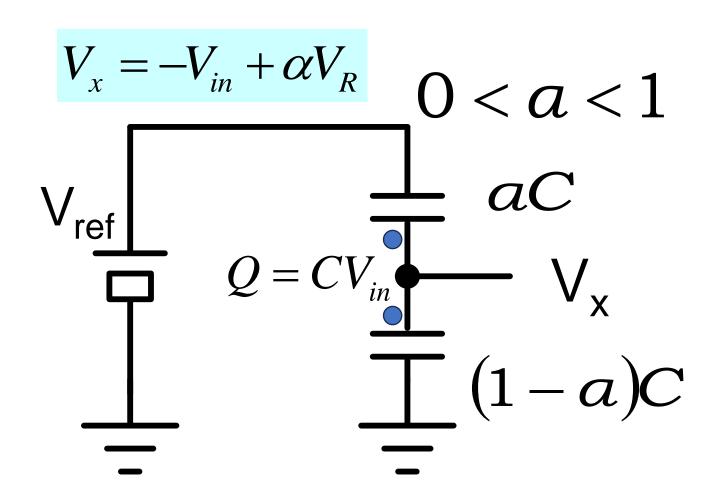

### SAR ADCにおける容量DACの役割

SAR ADCにおける容量型DAC (CDAC)は①容量に信号電圧に比例した電荷を保持するサンプリング機能と②一方の容量端子を参照電圧V<sub>ref</sub>もしくはGNDに接続する容量を切り替える電圧比較を行う。定常電流が流れず、低エネルギー動作。

① 信号の標本化と保持

② 信号電圧と重みを付けた参照電圧との比較

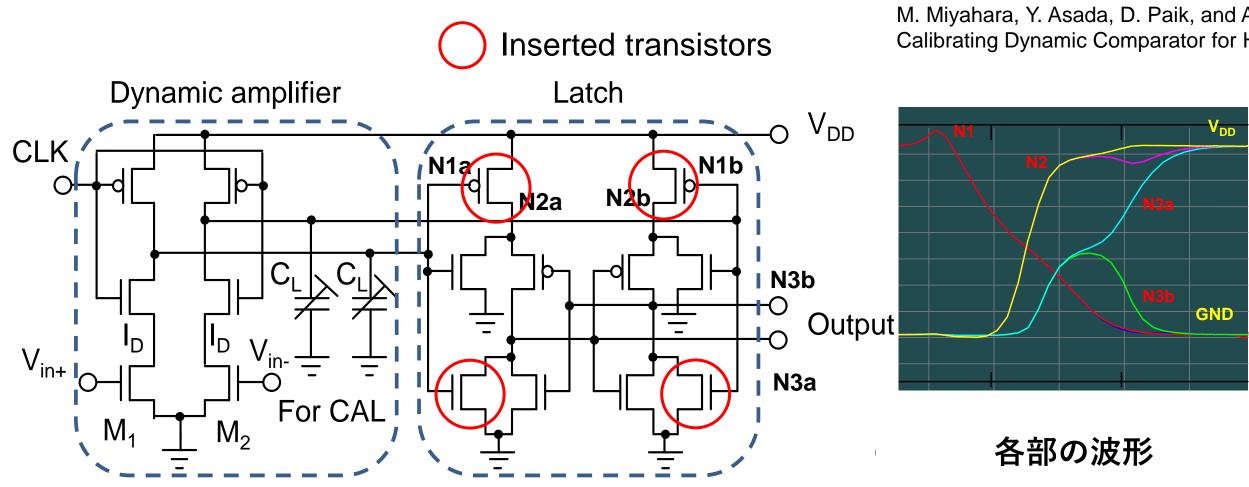

# 低ノイズダイナミック比較器の開発

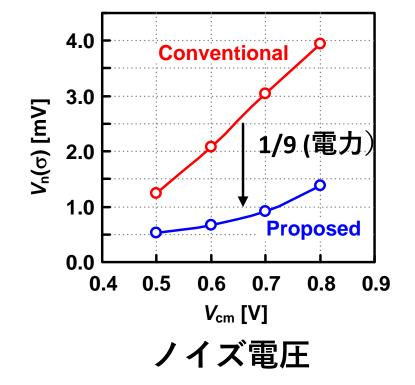

CMOS差動型F/Fの前段にダイナミックアンプを配したダイナミック型比較器は定常電流が流れないので極低エネルギーで動作し、4GHz程度の高速動作が可能だが、ノイズが大きく、SAR ADCは10ビット程度の分解能が限界であった。我々は段間にCMOSインバータを挿入してノイズ電力を1/9程度に低減し、12ビット分解能まで分解能を向上させた。

M. Miyahara, Y. Asada, D. Paik, and A. Matsuzawa, "A Low-Noise Self-Calibrating Dynamic Comparator for High-Speed ADCs," A-SSCC, Nov. 2008.

ダイナミック型比較器

# ダイナミックアンプの開発

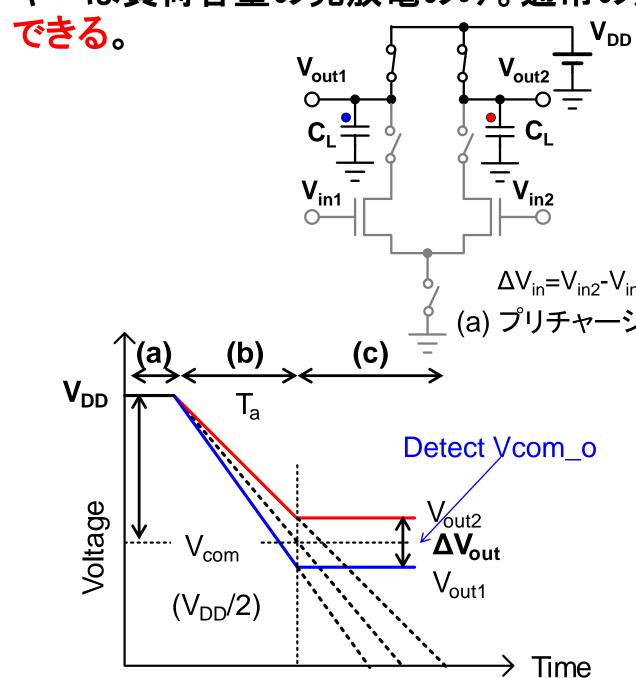

ダイナミックアンプは定常電流が流れず超低電力であり6倍程度の利得は実現できる。消費エネルギーは負荷容量の充放電のみ。通常の定常電流と負荷抵抗ではなく、容量とスイッチアンプでも増幅

$$\Delta V_{out} = \frac{\Delta Q}{C_L} = \frac{\Delta I_D \cdot T_a}{C_L} = -\frac{g_m \Delta V_{in} \cdot T_a}{C_L} \qquad T_a = \frac{C_L \left(V_{DD} - V_{com}\right)}{I_{DA}}$$

$$G_v \equiv \frac{\Delta V_{out}}{\Delta V_{in}} = -\frac{g_m \cdot T_a}{C_L} = -\frac{g_m \cdot \left(V_{DD} - V_{com}\right)}{I_{DA}} \qquad G_v = -\frac{2\left(V_{DD} - V_{com}\right)}{V_{eff}}$$

J. Lin, M. Miyahara and A. Matsuzawa, "A 15.5 dB, wide signal swing, dynamic amplifier using a common-mode voltage detection technique," 2011 IEEEI SCAS.

A. Matsuzawa

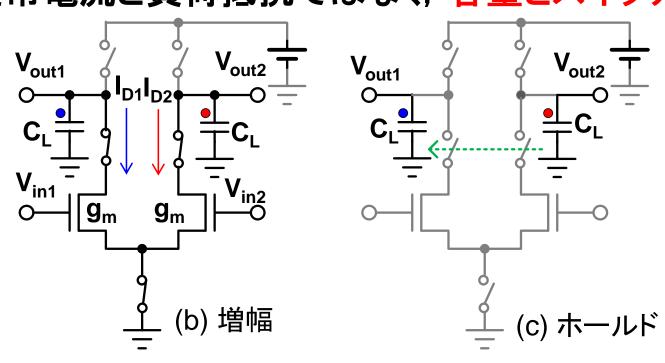

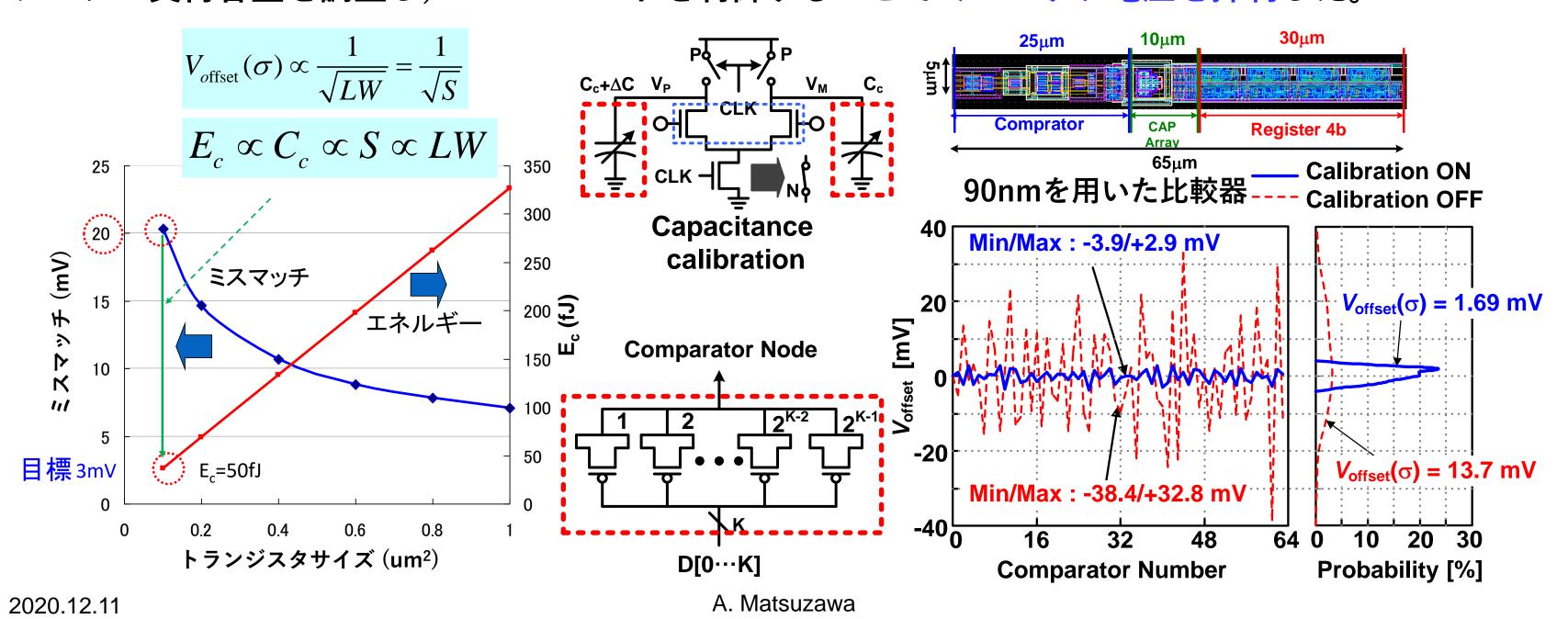

## 容量バンクを用いたミスマッチ補償回路の開発

素子の面積低減に伴いミスマッチ電圧が上昇し、精度が劣化する。素子を大きくするとエネルギー 消費が急増する。そこで、微細素子を用いてエネルギー消費をおさえ、ミスマッチはダイナミック アンプの負荷容量を調整し、スルーレートを制御することでミスマッチ電圧を抑制した。

### アナログコンピュータへの応用

AIや量子コンピュータはアナログコンピュータであり、演算をアナログで行うことで低エネルギー演算が可能である。I/Oはデジタルなので、最近、アナ・デジ混載技術のコンピュータ応用が盛んになっている。

### Digital computer

### Analog computer

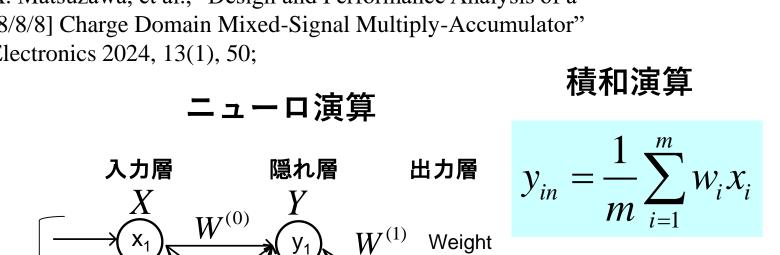

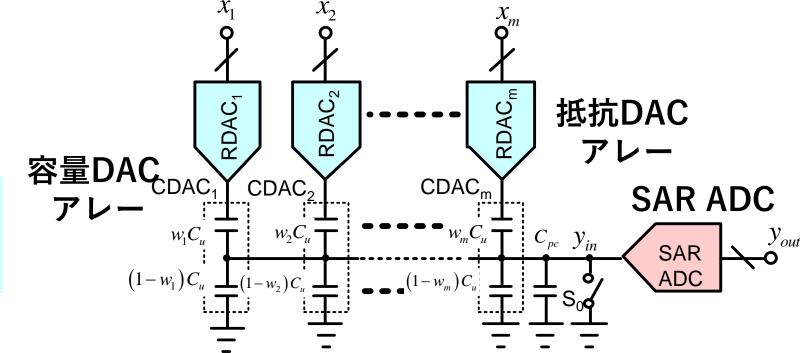

### 一例:電荷保存則を用いたアナ・デジ混在積和演算器

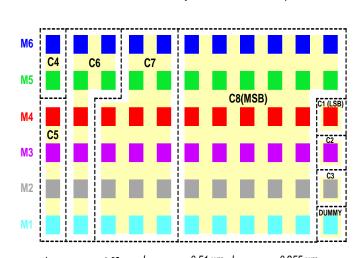

ニューロ演算(=積和演算)は電荷保存則を用いた演算で実現でき、抵抗DAC、容量DAC SAR ADCで構成できる

A. Matsuzawa, et al., "Design and Performance Analysis of a [8/8/8] Charge Domain Mixed-Signal Multiply-Accumulator" Electronics 2024, 13(1), 50;

Coefficient

出力

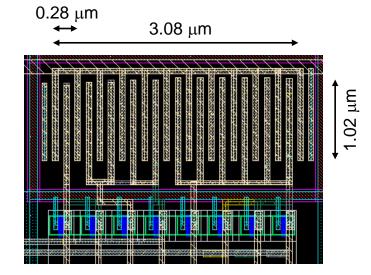

#### 8bit容量DAC(平面図)

#### 容量DAC(断面図)

$L_{FINGER\ C3-C8} = 1.02\ \mu m$   $L_{FINGER\ C2} = 0.51\ \mu m$   $L_{FINGER\ C1} = 0.255\ \mu m$

A. Matsuzawa

入力

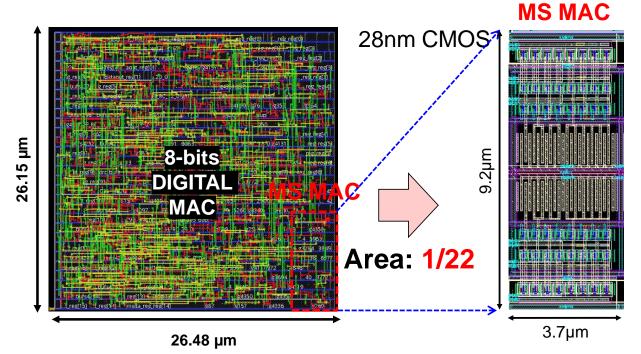

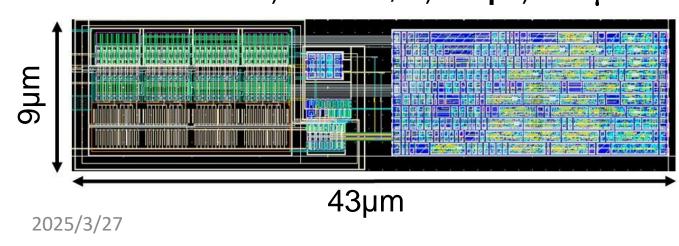

## 電荷保存則を用いたアナ・デジ混在積和演算器

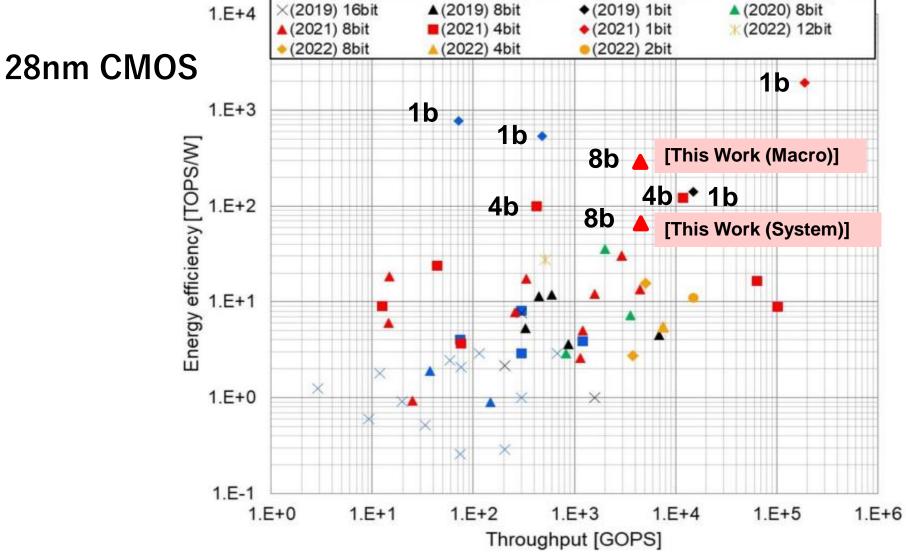

[8, 8, 8]の積和演算器を試作し、180MHz動作を240TOPS/Wの超低エネルギーで実現。

デジタル回路に対して1/75のエネルギー, 1/22の面積

8ビット精度で最高の演算効率を実現

• (2016-2018) 1bit

NN Performance and Efficiency

SAR ADC 8b, 200Ms/s, 0.8pJ,  $140\mu$ W

### まとめ

電子機器の発展と変遷および、バイポーラ、Bi-CMOS, CMOSなどのデバイスの変遷に伴うADC技術の歴史と発展について概観。

連続時間型から離散時間型アナログ回路へ、更に定常電流が流れず、超低エネルギーで動作するダイナミック型アナログ回路へ変遷。

素子の面積低減に伴い精度が劣化、精度確保のためのチョッパーや補間技術やキャリブレーション技術、低電力化技術を開発。DVDのワンチップアナ・デジ混載システムLSIを可能にした。

CMOSロジック回路のようにスケーリング則が適用可能で、微細化により一層の高速化と低電力化が可能となった逐次比較型ADC によるインターリーブ動作により100Gs/s の超高速デジタル光通信を可能に。

AIや量子コンピュータという先端アナログコンピュータ技術にとってもADC技術が重要。