日時

会場

主催

共催

講演

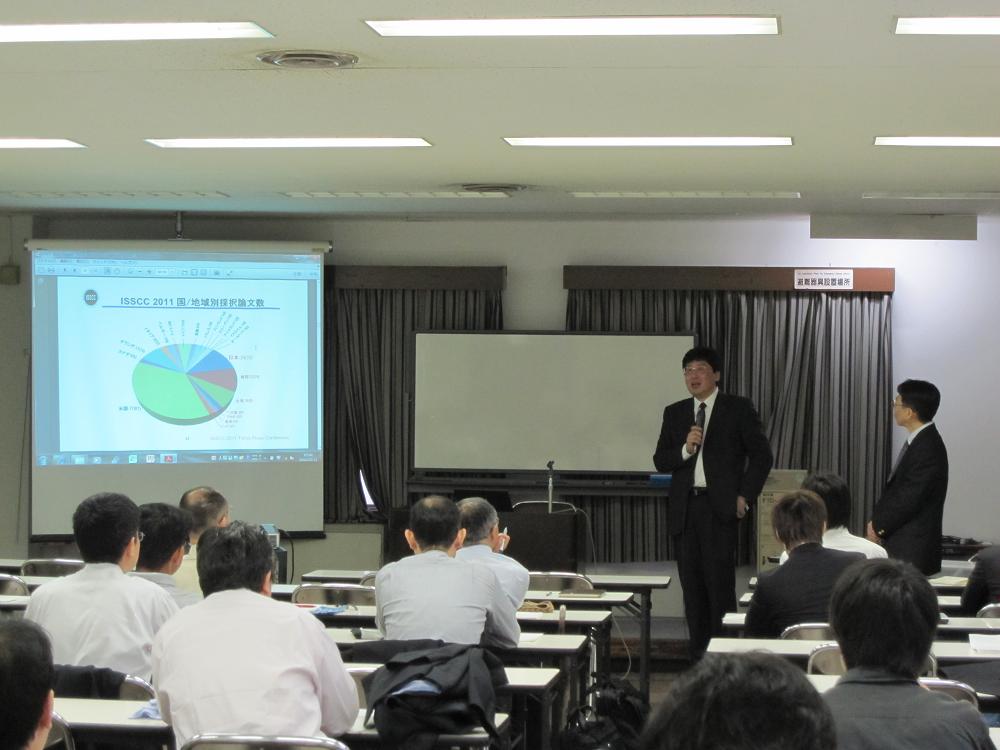

ISSCC 2011 レビュー講演

ISSCC 2011 レビュー講演Dr. Hideto Hidaka, Renesas Electronics,

ISSCC 2011 Program Vice Chair

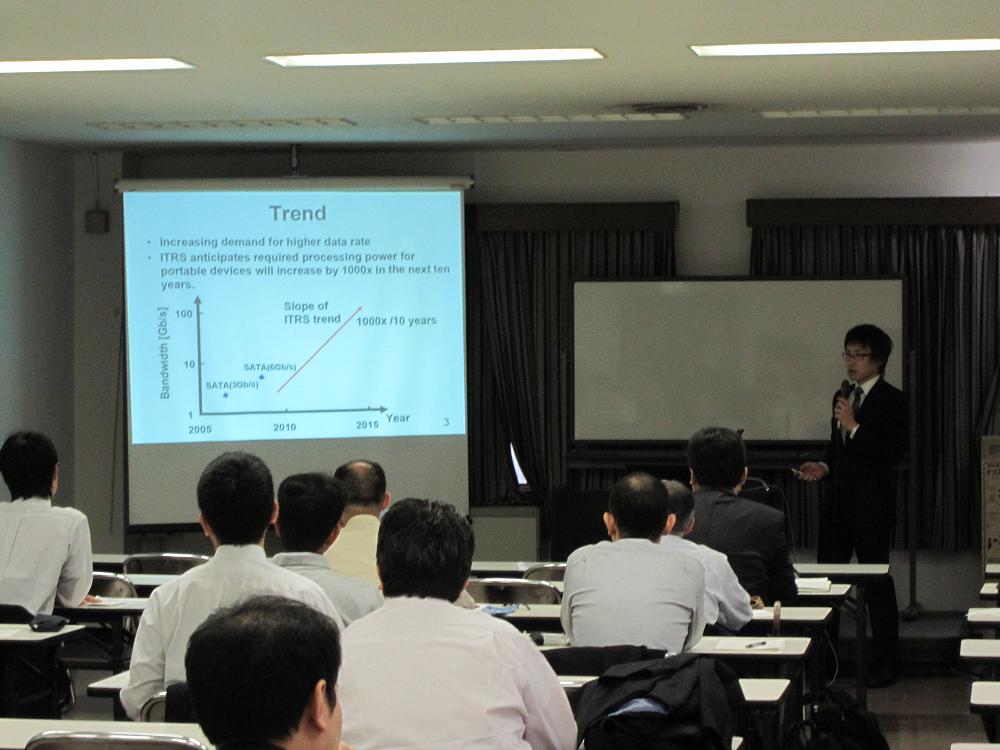

"A 12.5+12.5Gb/s Full-Duplex Plastic Waveguide Interconnect"

S, Fukuda, Sony

TA 12.5+12.5Gb/s full-duplex low-power millimeter-wave-based end-to-end dielectric waveguide interconnect solution with an active footprint of 0.40mm² is demonstrated in 40nm CMOS. A pair of twocarrier transceivers operating simultaneously at 57GHz and 80GHz achieves a full-duplex connection over a 120mm plastic waveguide with a BER of less than 10^-12.

"10:4 MUX and 4:10 DEMUX Gearbox LSI for 100-Gigabit Ethernet Link"

G. Ono, Hitachi

A 2W 100Gb/s Ethernet gearbox LSI combining a 10:4 MUX and a 4:10 DEMUX in 65nm CMOS is presented. Replacing current-mode logic circuits with CMOS circuits by decreasing clock frequency and effective circuit-operation speed reduces power by 75% compared to that of a conventional LSI. The 25Gb/s interface in the LSI achieves BER < 10^-12 with 34.3mVpp input sensitivity

"A 570fs-rms Integrated-Jitter Ring-VCO-Based 1.21GHz PLL with Hybrid Loop"

A. Sai, Toshiba

A 1.21GHz PLL with a hybrid loop consisting of a type-II all-digital PLL and a type-I analog PLL is presented. The analog PLL with a divider-less 3-input PFD suppresses the phase noise of a ring digital/ voltage-controlled oscillator within the loop bandwidth. The PLL achieves the integrated rms jitter of 570fs, draws 43mA from 1.2V supply and occupies 0.12mm² in 65nm CMOS

"95%-Lower-BER 43%-Lower-Power intelligent Solid-State Drive (SSD) with Asymmetric Coding and Stripe Pattern Elimination Algorithm"

K. Johguchi, University of Tokyo

SSD techniques are presented that result in 95% lower bit-error rate and 43% lower power. It is shown that the memory cell errors in data retention and program disturb as well as the power consumption strongly depend on the data pattern. Asymmetric coding reduces the population of high VTH states to decrease the cell error by 95%. A stripe pattern elimination algorithm saves bitline charging and reduces the power by 43%.

"A 95mV-Startup Step-up converter with VTh-Tuned Oscillator by Fixed-Charge Programming and Capacitor Pass-on Scheme"

P-H. Chen, University of Tokyo

A 95mV startup-voltage step-up converter with capacitor pass-on scheme for energy-harvesting applications is described. The post-fabrication VTH trimming improves the minimum operating voltage of the clock generator at startup. The step-up converter achieves the low startup voltage in standard 65nm CMOS without mechanical assist.

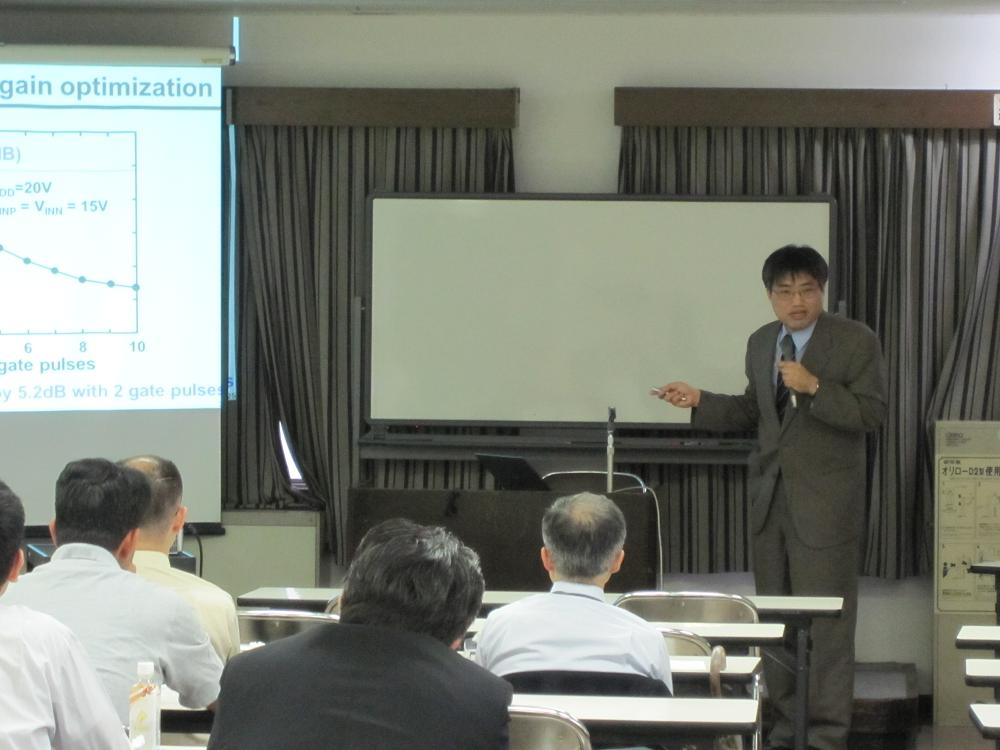

"100V AC Power Meter System-on-a-Film (SoF) Integrating 20V Organic CMOS Digital and Analog Circuits with Floating Gate for Process-Variation Compensation and 100V Organic PMOS Rectifier"

K. Ishida, University of Tokyo

A system-on-a-film integrating: i) 20V organic CMOS opamp with variation-compensation capability, ii) 20V organic CMOS frequency divider with high-gain pseudo-CMOS inverters, iii) 100V organic PMOS rectifier for generating 50Hz clock and 20V DC power is developed for realizing a 100V AC power meter.

"Real-Time Current-Waveform Sensor with Plugless Energy Harvesting from AC power Lines for Home/Building Energy-Management Systems"

S. Takahashi, NEC

A TX-integrated battery-free current-waveform sensor with plugless energy harvesting from AC power lines is fabricated in 90nm CMOS with 560×300um². A realtime sampler that use a half cycle timeto- digital convertor and RF-power-management to enable -5.5dBm RF power at the 50kS/s with a harvesting power supply of 1mW.

"A 12Gb/s Non-Contact Interface with Coupled Transmission Lines"

T. Takeya, Keio University

The paper describes a high data rate non-contact memory card interface using a single channel. The wideband channel based on differential coupled transmission lines achieves measured coupling level of 16dB and a bandwidth from 2.6 to 9GHz. The system achieves 12Gb/s with BER<10^-13 at a communication distance of 1mm.

"A 16Mfps 165kpixel Backside-illuminated CCD"

T. Etoh, Kinki University

A 362×456, 43.2um pixel pitch, 16Mfps, backside-illuminated CCD storing 117 consecutive images recorded with charge carrier multiplication achieves image capture capability with less than 9photons/pixel. The full well capacity of 8,000e- at 16Mfps and 22,000 e- at 4Mfps is realized.

"A 300mm Wafer-Size CMOS Image Sensor with In-Pixel Voltage-Gain Amplifier and Column-Level Differential Readout Circuitry"

S. Kikuchi, Canon

A 1.6Mpixel, 202×205mm² CMOS image sensor on 300mm wafer consists of pixels of 160um pitch with a 0-to-24dB variable gain in-pixel voltage amplifier. Reset and integrated signals are simultaneously read out from the pixel through a pair of column lines. It achieves a sensitivity of 25Me-/lux-s, random noise of 13e-rms and operates at 100fps with global synchronous shutter.

参加者

講演者と役員