Sep. 14 '06 SSCS Kansai

## <u>– Trend of Advanced SiP –</u> <u>–Technology Development –</u>

## Renesas Technology Corp. System Solution Business Group Takafumi Kikuchi

Everywhere you imagine. **RENESAS**

©2006. Renesas Technology Corp., All rights reserved.

Rev. 1.00 00000-A

## **Contents**

- **1. Semiconductor in Ubiquitous Network Era**

- 2. Approach for System Solution

- **3. SiP Solution with SH-Mobile**

- 4. SiP Solution with DSC

- 5. Renesas SiP Consistent Design

- 6. Design for SiP

- 7. SiP Design technology for High Speed I/F

- 8. SiP Mounting Technology

- 9. Stack SiP Development Trend

- **10. SiP Technology for Next Generation**

- CoC Technology -

- **11. Next Generation SiP Technology**

- Si Hole-Through Technology-

# 1. Semiconductor Needs for Ubiquitous Network Era

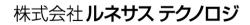

#### Macro trend of growth rate at Semiconductor Market

The rate of market growth is tend to become slow Action item is Determination of

**"The Next Generation Growth Market" and Resource Concentration**

**\***CAGR is calculated after it approximates in order to decrease influence to Silicon Cycle.

Ref. :WSTS(2005.10)

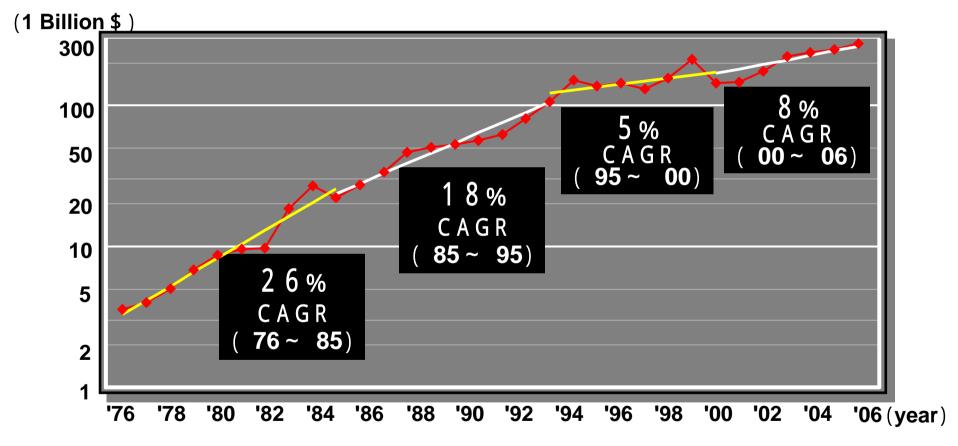

### **Classification of Application and Convergence**

Developing function convergence such as Multimedia Processing and Network. Continuity and development of Excellent Hard IP and Software IP become Important.

©2006. Renesas Technology Corp., All rights reserved.

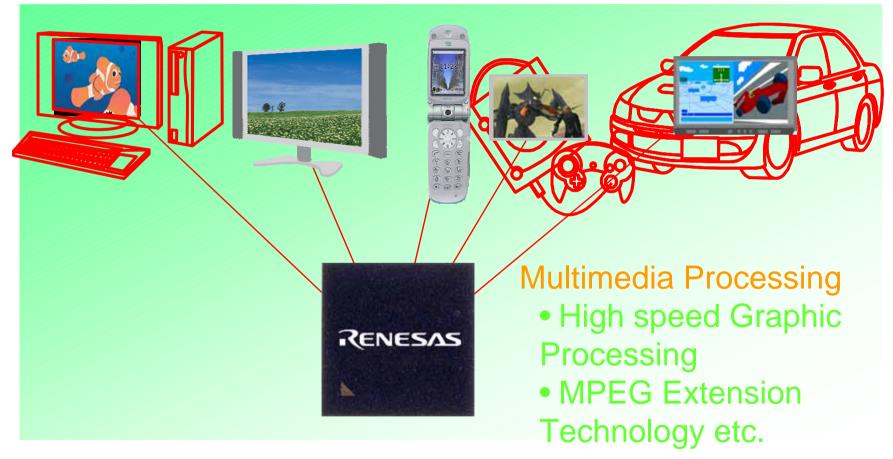

#### **Huge Expansion of Application Software Development**

#### **Progressing Expansion of Software Development**

in Ubiquitous Network Equipment

Source : IPA Information Processing System Society of Japan embedded system research Gr establishment commemoration symposium (July, '05)

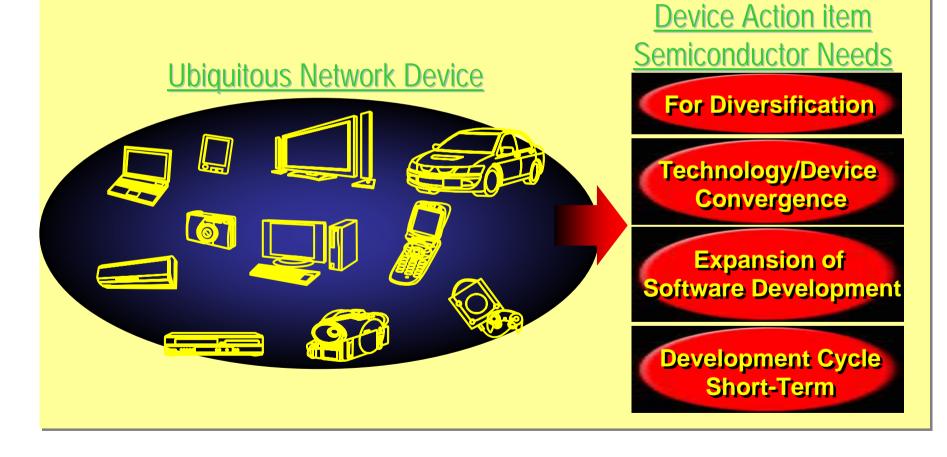

# **Action item of Semiconductor System Solution**

"Diversification", which is Action item of Ubiquitous Network Equipment Semiconductor is required revenge of "Convergence", "Development Expansion of Software", "Short-term Development Cycle"

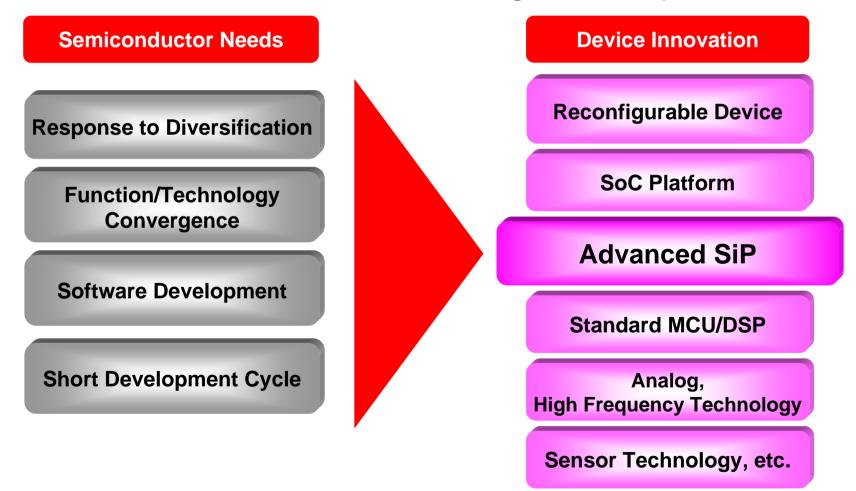

## Device Innovation which realizes semiconductor needs in the ubiquitous generation

SoC Platform and Advanced SiP get more important

## 2. Approach toward System Solution

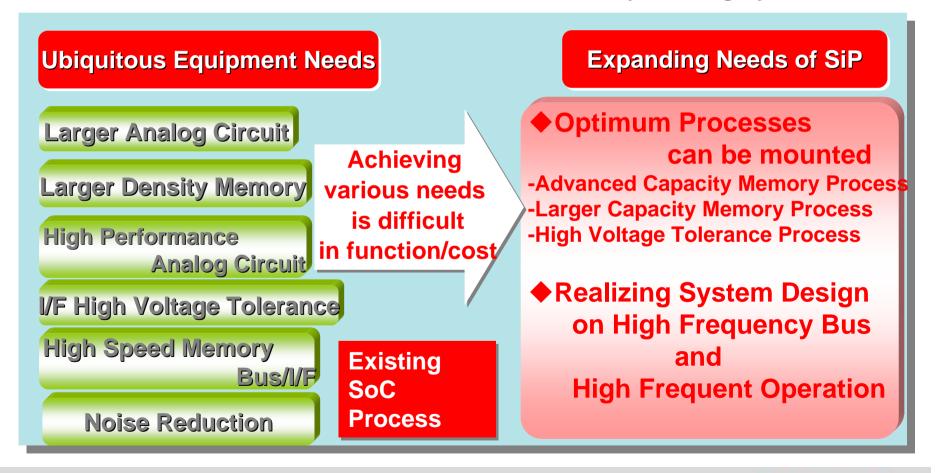

#### **More Difficult Needs for SoC to Realize**

- Larger Capacity Memory, High Frequency Bus and High Performance Analog Circuit are Required to Realize Ubiquitous Equipment

- Realize the best solution with SiP to combine High Powered SoC, Mass Memory and Highly Accurate

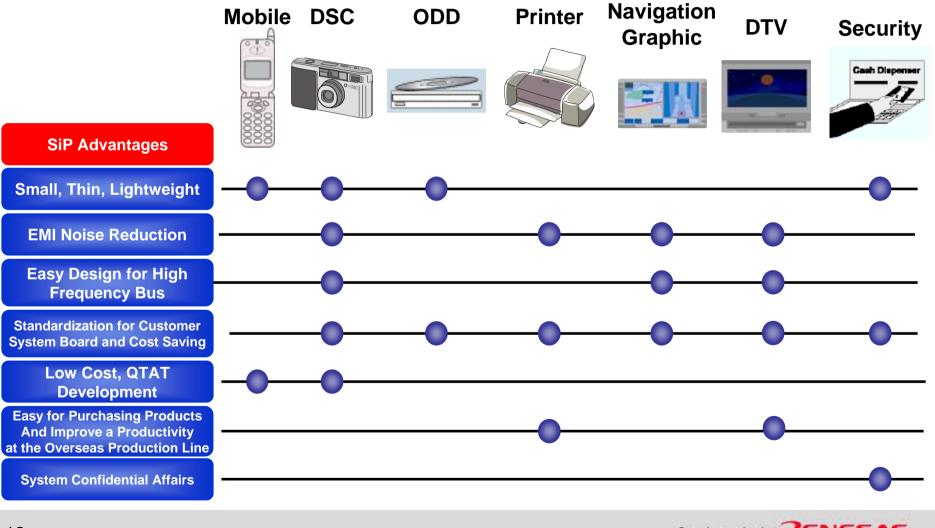

#### **SiP Technology Realizes Various Application Needs**

#### ~ SiP Realizes Various Advanced Applications ~

### Advancing SiP Technology to realize Multi Function and High Powered

**Request to SiP**

High-Powered System, Muti Function

Achievement of Best and Low Cost SiP

Small, Thin, Higher Heatproof inclination

Large Capacity, High Speed Memory

Remain High reliability as single chip Corresponding SiP technology and approach

High-Speed I/F(DDR), Noise Reduction, Analog

**Design for SiP** (DFS)

High Density SiP Mounting Technology

KGD<sup>,</sup> Multi Bit Bus Memory, Tie-up with Memory Supplier

**Optimization of test process**

\* KGD-Known Good Die

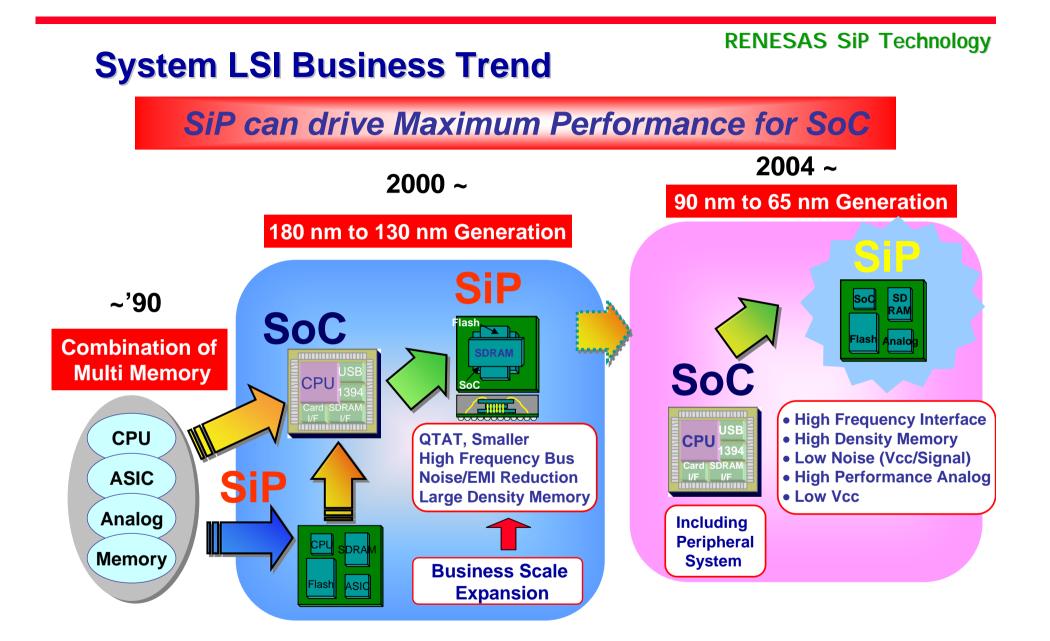

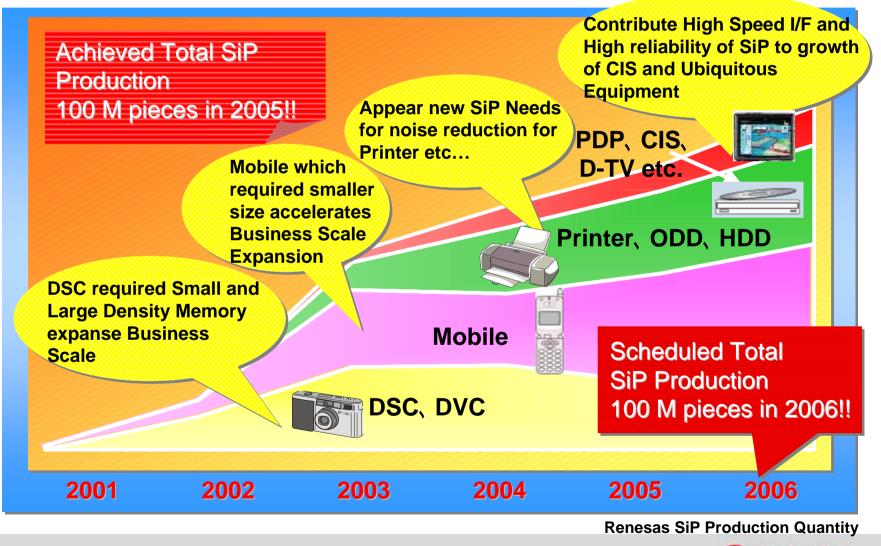

#### **Renesas Leading SiP Market**

Making to high performance and the SiP technology of the application alternately pull the market growth.

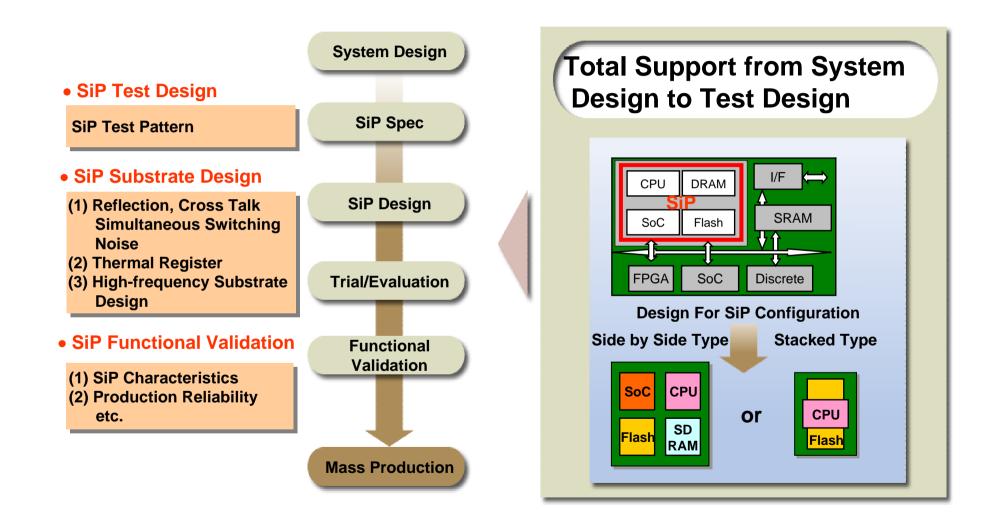

## 5. Renesas SiP Consistent Design System

### **SiP Consistent Design System**

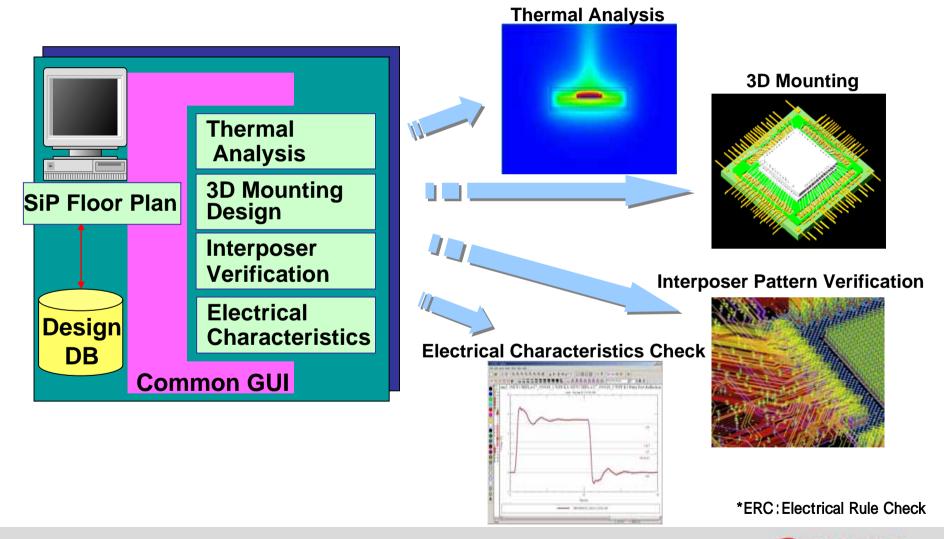

### SiP integration design environment

**Design Quality Improvement**

#### by Electrical Characteristics Check and Verification

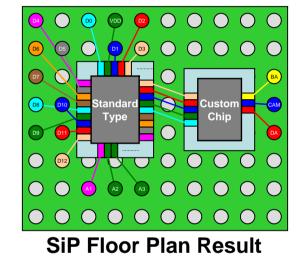

#### **SiP Floor Plan**

**Our Goal:**

SiP Design Which Fulfills the Performance, Power, Cost, PKG Size and Pin Numbers

- SiP Floor Plan

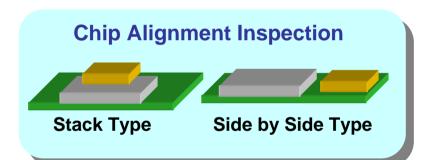

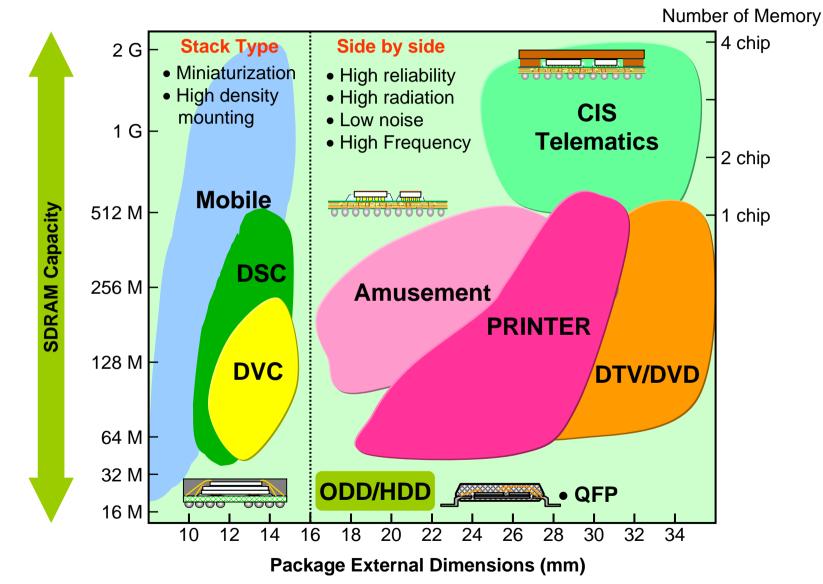

- 1. Decision on Mounting Type (Stack Type or Side by Side Type)

- 2. Decision on Chip Alignment with Considerations of Simple Substrate Pattern

#### **Examination of Simple Substrate Pattern (1)**

#### **Examination of Simple Substrate Pattern (2)**

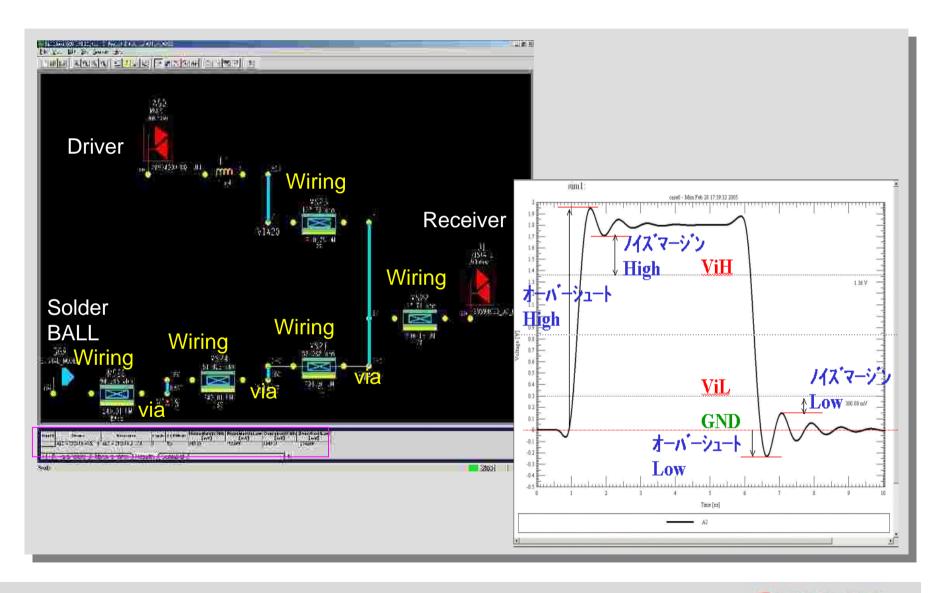

#### RENESAS SiP Technology Example of chip interconnection SI analysis result

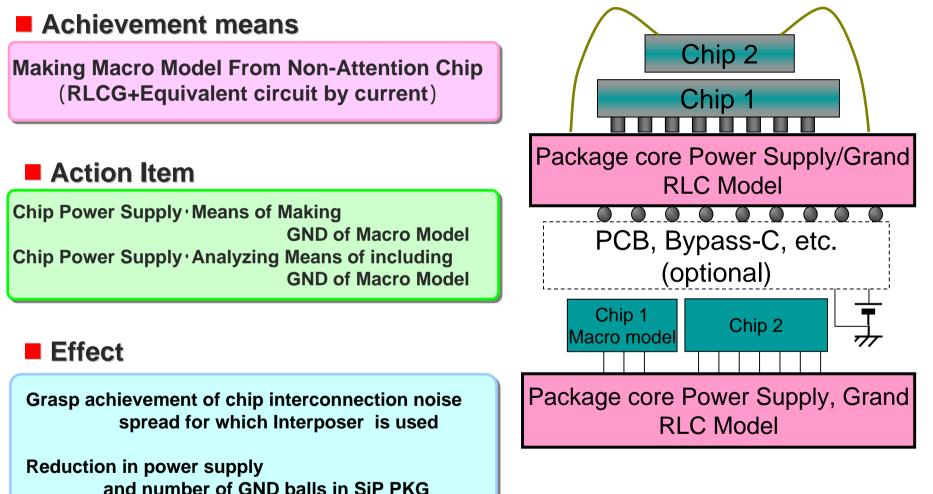

## IR-drop Analysis Enhancing Technique Examination for SiP

#### **SiP Simulation Cases**

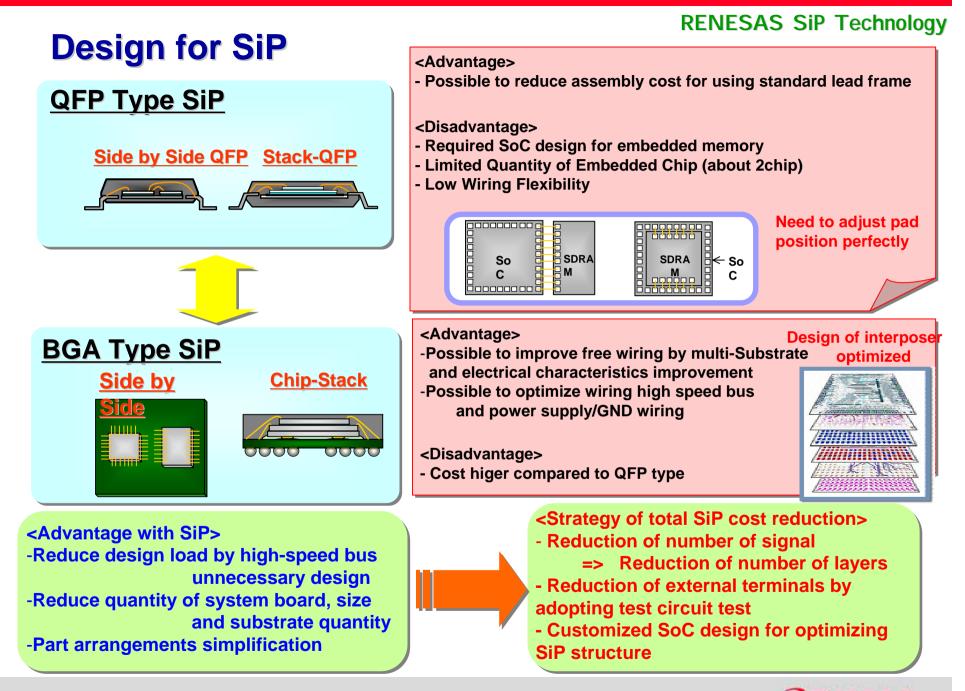

## 6. Design for SiP

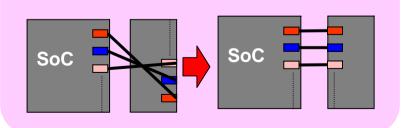

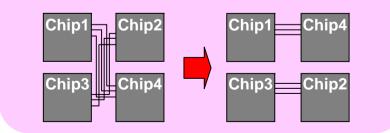

#### **RENESAS SiP Technology** SoC design to consider SiP (Design For SiP) - Realize Suitable SiP Structure $\Rightarrow$ Consideration cost for SiP Design Technology -[1] Optimization of Chip Configuration [2] Optimization of I/O Pad Arrangement Before Optimization Upper Chip After Optimization **Before Optimization** Upper Chip Less SiP Substrate Lavers Many SiP Substrate Layers Lower Chip Spacer 4 or Less Lavers. More Layers, Must use B/U Substrate Lower Chip Able to use Glass Epoxy A-A' Cross-section **Spacer Needed** Α' A Chip B Chip A Chip B Chip After (SoC) Memory (SoC) Memorv) **Optimization** A otimizatio Upper Chip Π Lower Chip Upper Chip Lower Chip A-A' Cross-section Complicated Wiring Net St P SiP . ۷ Spacer is no Longer Needed [4] Embedded Test Circuit Saves [3] Optimization of I/O Buffer Drivability the Number of External Terminals Wiring on the Substrate Embed a Test Circuit on Chips Long/Short Wire **Conventional** under Development Less Parasitic Components A Chip B Chip A Chip B Chip Increase Noise (SoC) A Chip 📑 B Chip (SoC) (Memory) Memory Difficulty with SI Management (SoC) Memory Effect B п BIST P в Lower I/O Electric Power **Circuit** в Reduce Simultaneous SiP Switching Noise SiP SiP Better SI Management by Optimizing Signal Terminals Used Only in SiP **Output Test Results Buffer Drivability** (Ex. Memory Bus) Reduce External Terminals **Input Special BIST Circuit Output All signals**

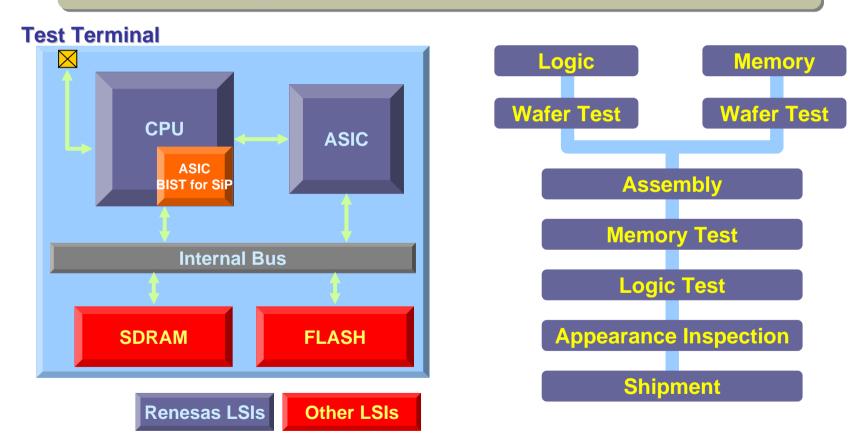

### **SiP Test Strategy**

#### Quality Guaranteed by RENESAS Original Testing Method

#### **SiP System Test with Test Terminal**

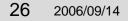

## 7. SiP Design Technology for High Speed I/F

### **Noise Problem of Speed-up and Mounting System**

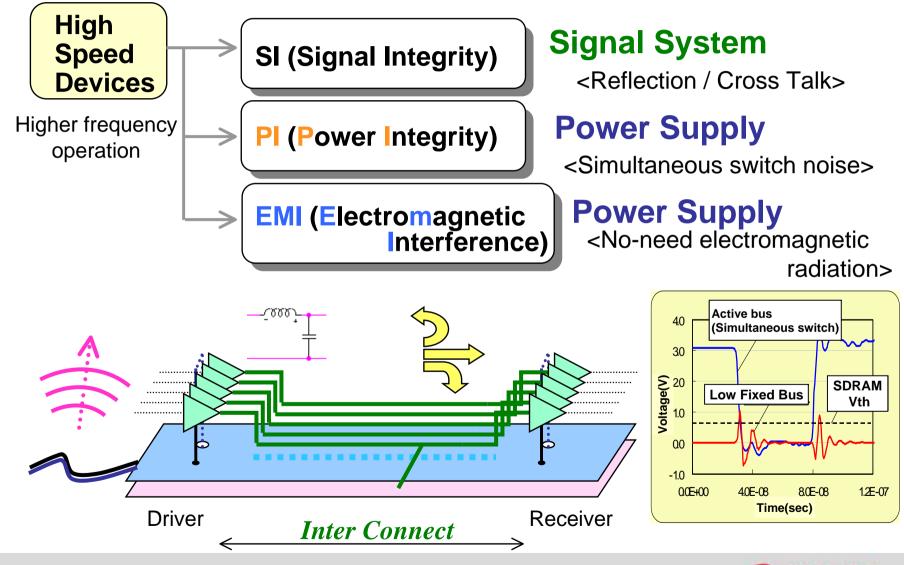

### **SiP Product Roadmap for High Speed**

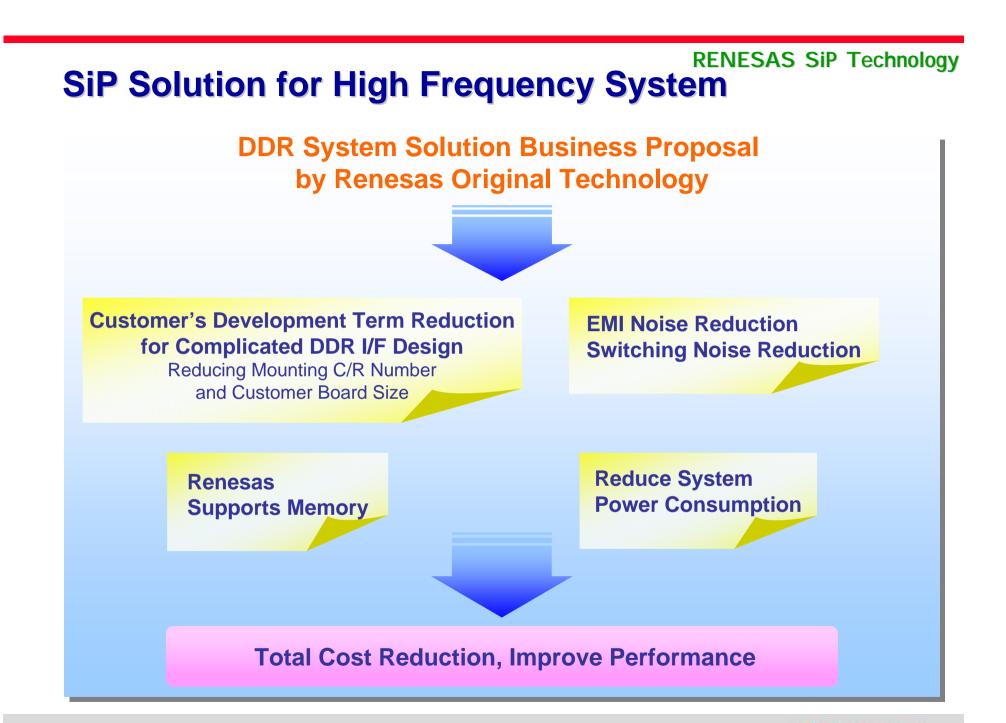

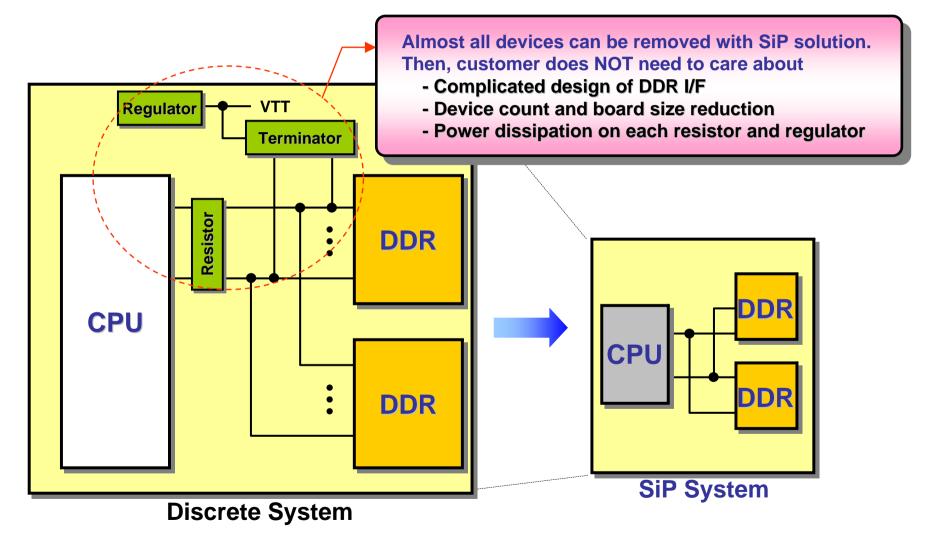

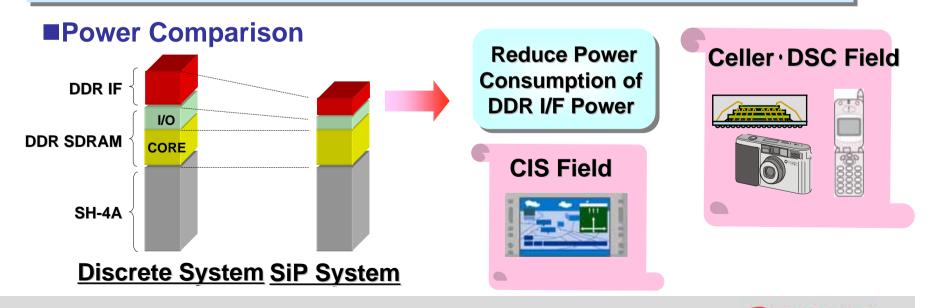

### Easy DDR System Design by SiP

#### Renesas SiP makes customer free from the design of complicated DDR I/F

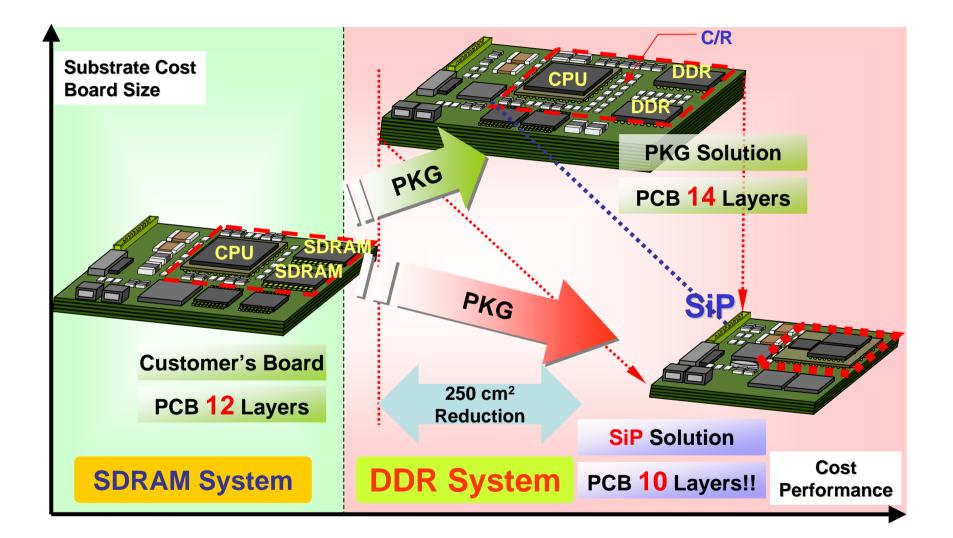

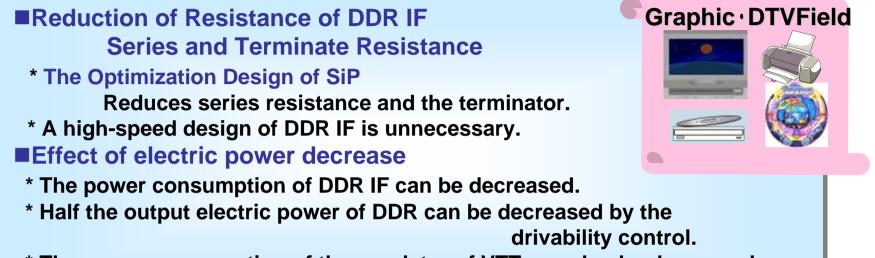

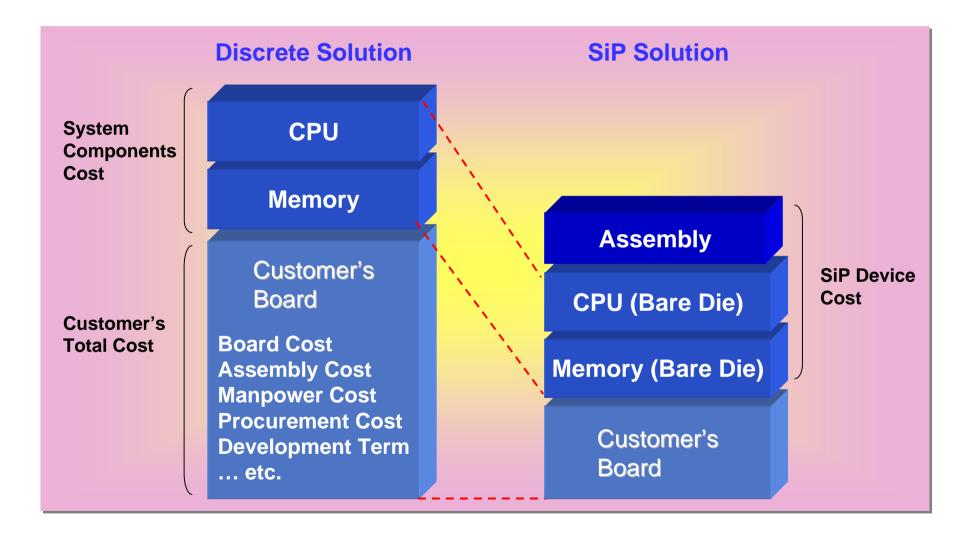

#### **Total System Cost Advantage of SiP DDR**

#### The strengths based on DDR-System

\* The power consumption of the regulator of VTT can also be decreased.

#### SiP can save Customer's Total System Cost

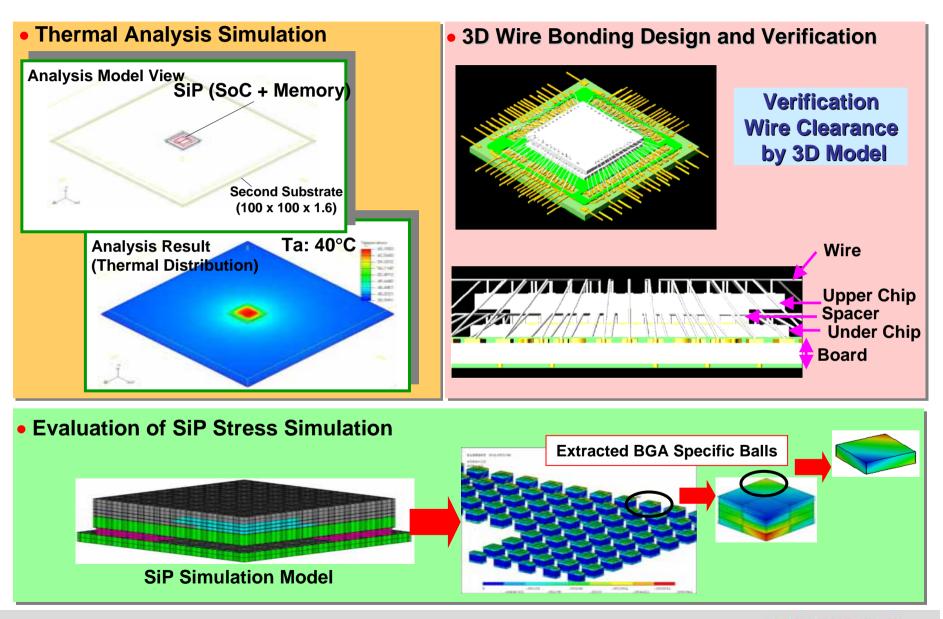

# 8. SiP Mounting Technology

### **Required Memory size by Application**

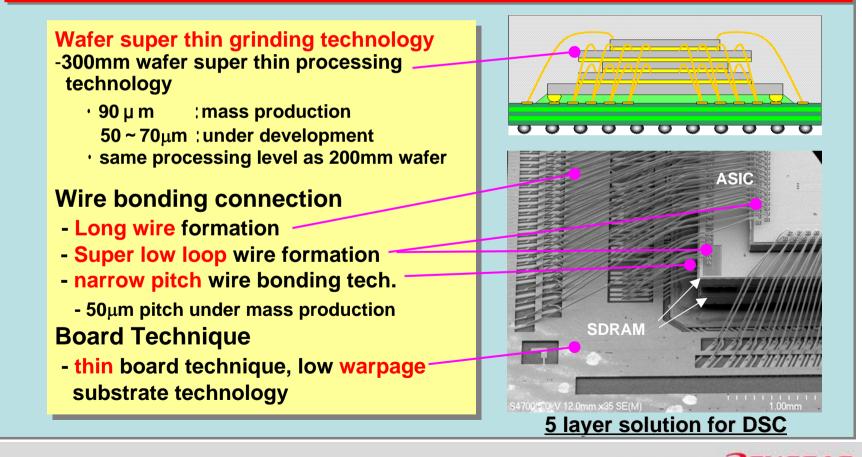

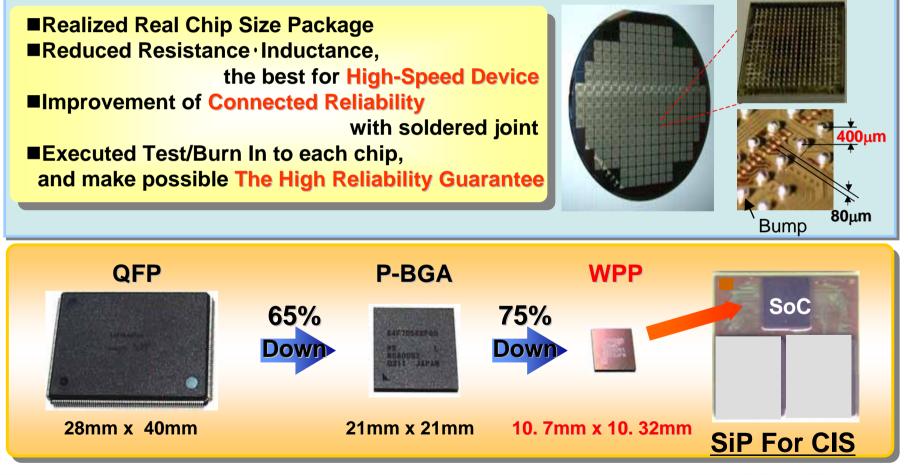

# **Technology to realize miniaturize and high quality**

Applied the result of the top-level world research

to the mounting technology.

Support from design to mass production

by mounting technology as the ITDM manufacturer

~ Realization of small size/high density SiP by FC technology + WB technology ~

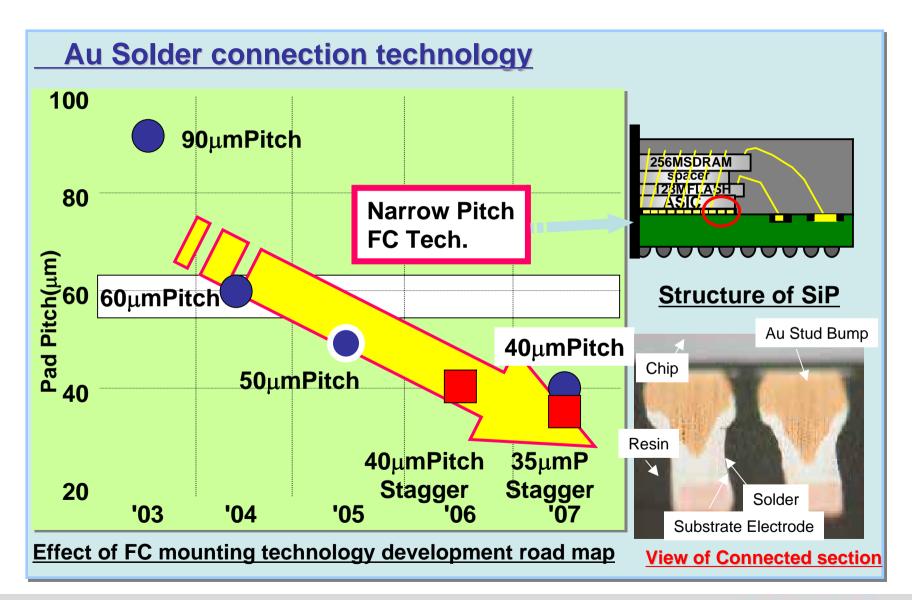

## The Trend of FC (flip chip) Technology

## Renesas SiP Highly Reliable Flip-Chip Connection Technology

~ RENESAS Original Highly Reliable Technology by WPP Technology ~

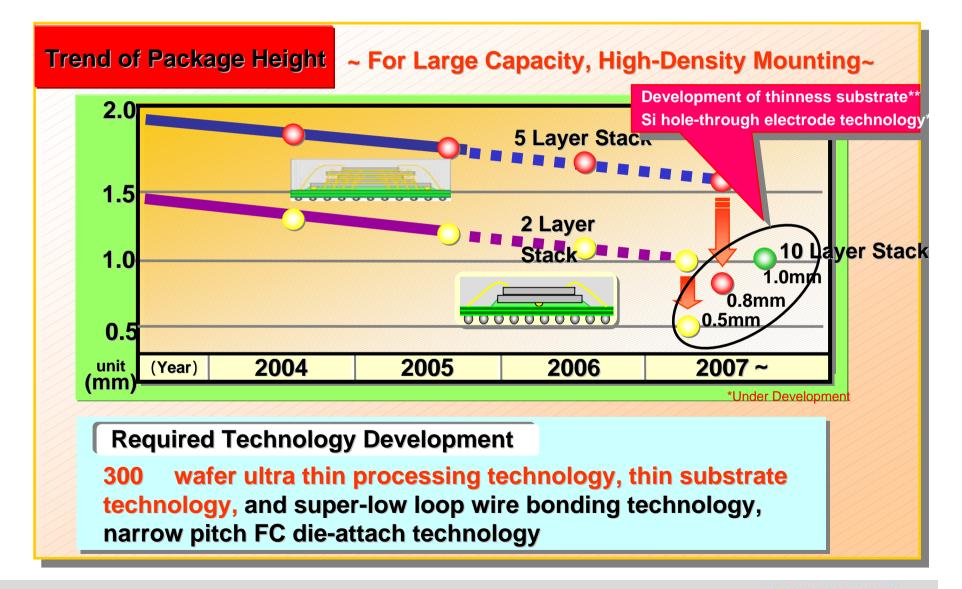

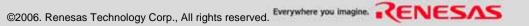

### **Super Thin Stack SiP Trend**

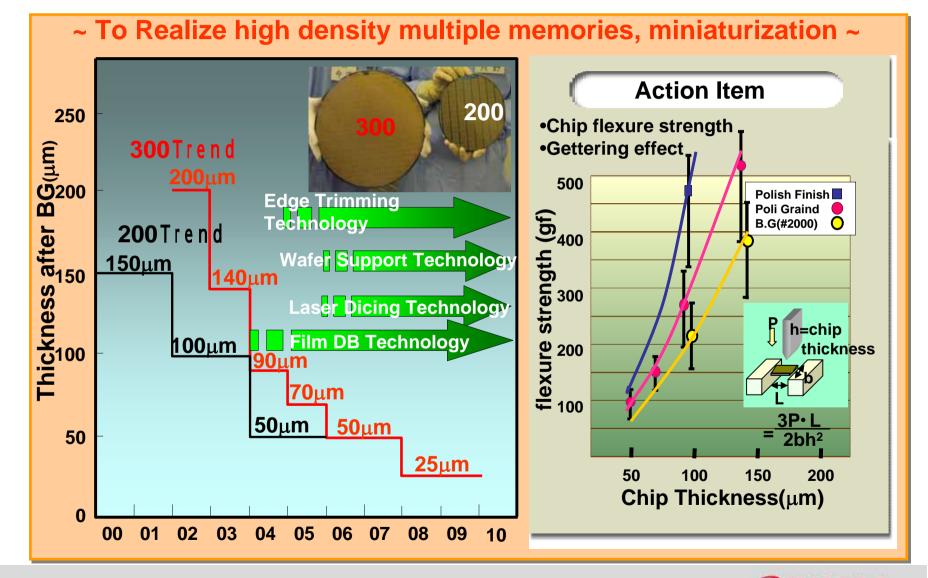

# BG(Back Grind) Processing Technology and DB Technology Development Road map

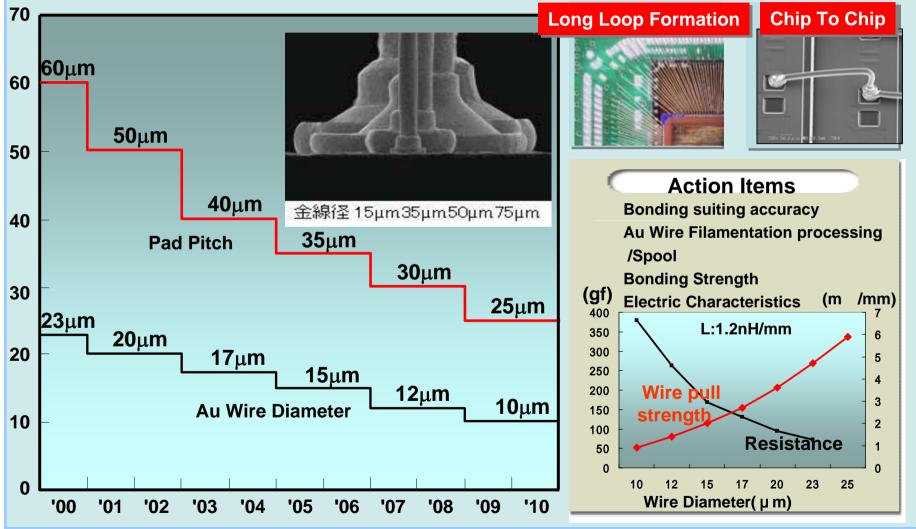

## **Road Map of Wire Bonding Technology**

Development

~ For Achieving Complicated Wire Formation ~

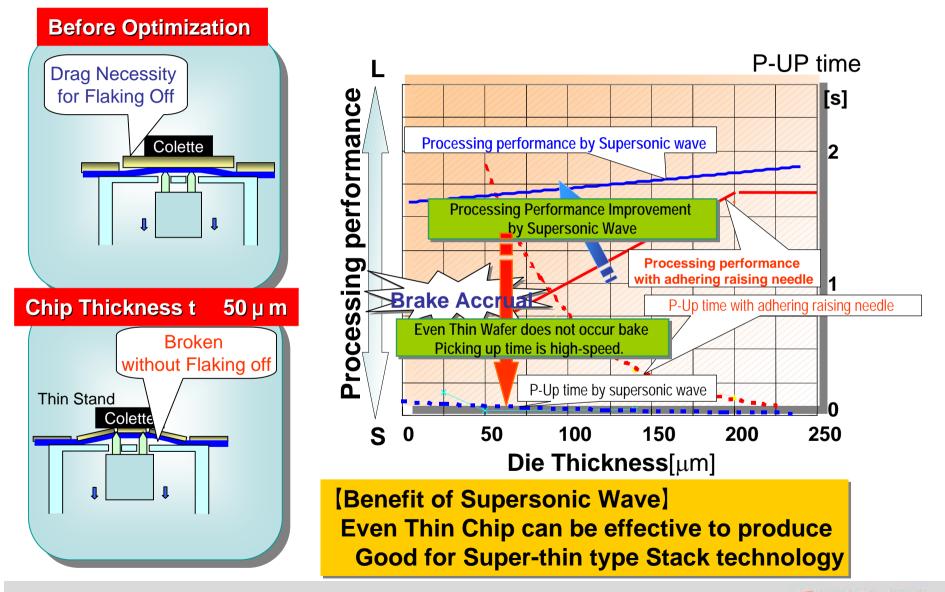

### **Thin Wafer Pick-Up Technology**

Examination of picking up technology with supersonic wave

# 9. Stack SiP Development Trend

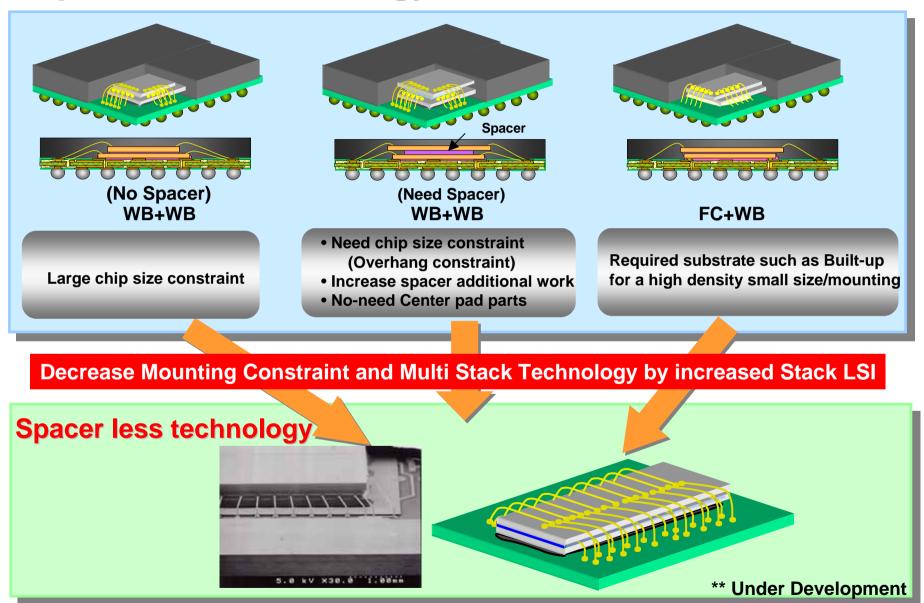

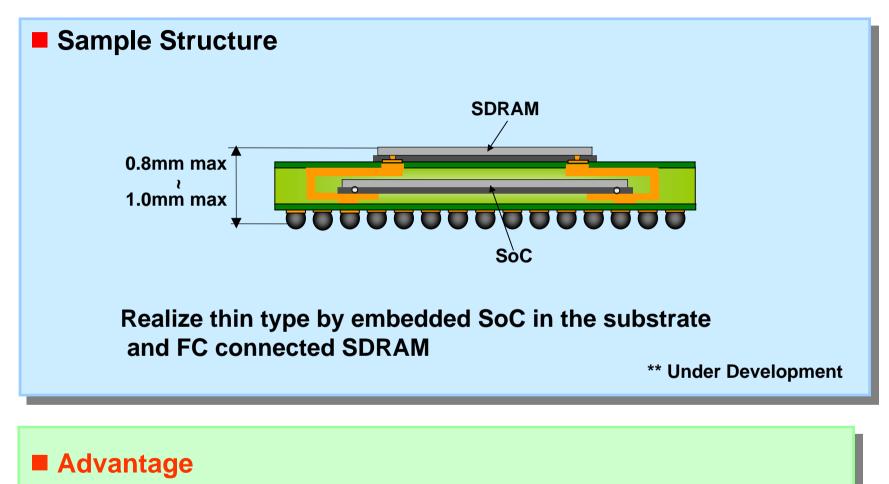

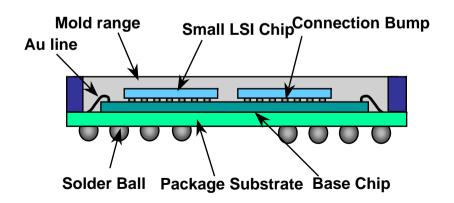

### **Spacer less Technology\*\***

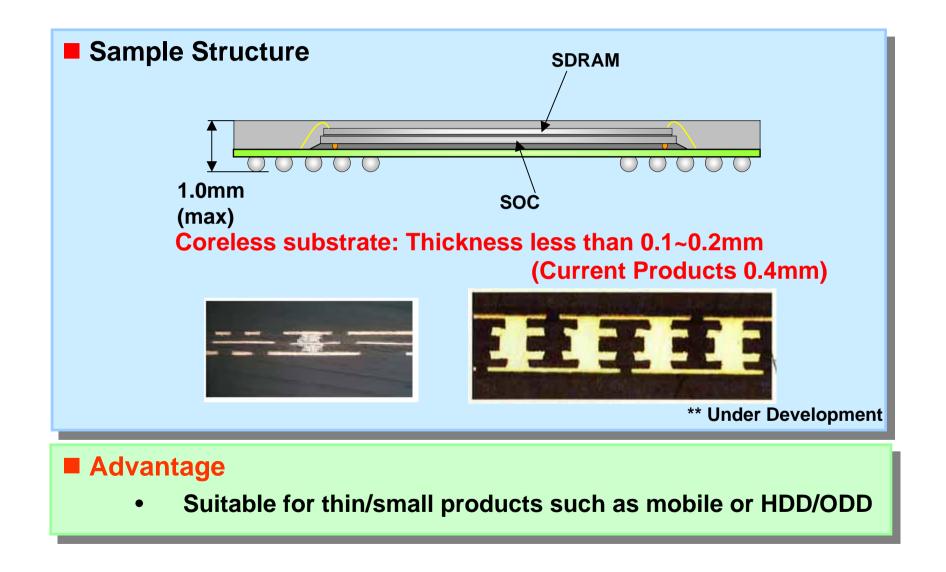

#### Thin SiP substrate\*\*

### LSI embedded substrate SiP\*\*

- Available for system black box such as security field

- Possible to make high density memory

### **PoP(Package on Package) Technology\*\***

## 10. Next Generation SiP Technology (CoC Technology)

# Benefits of CoC Technology(Chip on Chip)

Interchip High-Speed Data Transfer

(CPU-Memory etc.)

- Various kinds device consolidation SiP

- Process Consolidation of Various generation

(maturity + point)

- High density mounting

- Thin making multi chip accumulating PKG

When Base Chip is global wiring Chip

Minute wiring is unnecessary

Low Cost and Low resisted.

When Base Chip is LSI Chip

- mass memory installable

- Global wiring short able

Improved Switching Characteristics

- Unnecessary output buffer

**Reduced Power consumption**

After installed Base Chip, it can be tested.

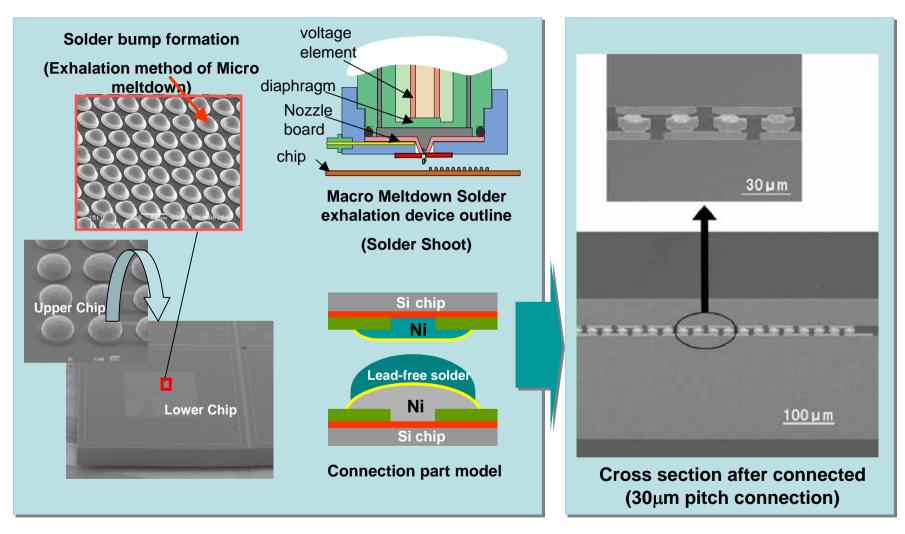

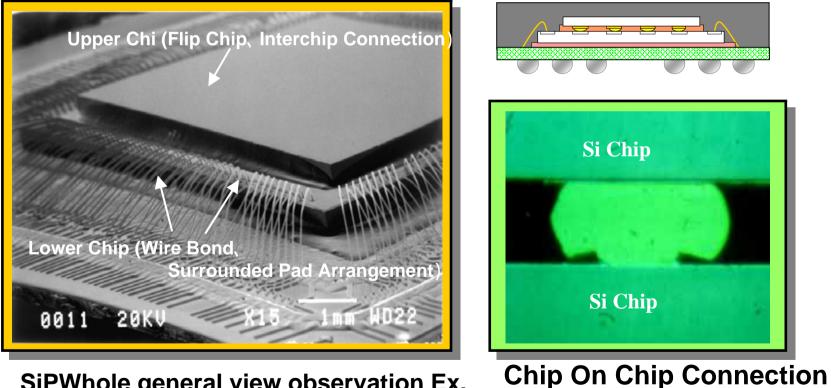

#### Minute pitch connection for CoC Technology

#### CoC (Chip on Chip) Connection COC(10,000bump)

## **Technology of Chip to Chip**

Substrate NET Reduction by LSI Development only for SiP For High-speed Operation

(Improvement of data Transfer rate)

#### **Digital and Analog Separation (Point SoC**

Achievement by SiP)

SiPWhole general view observation Ex.

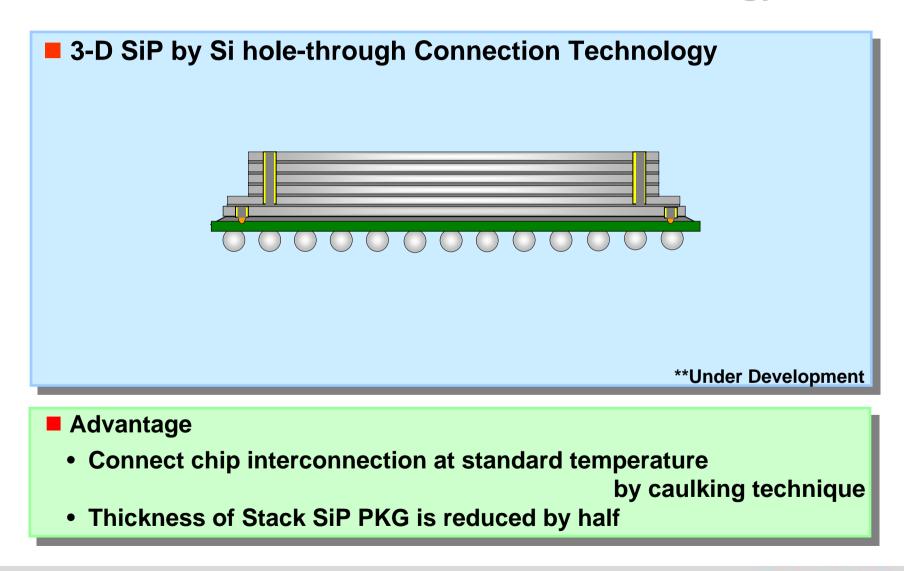

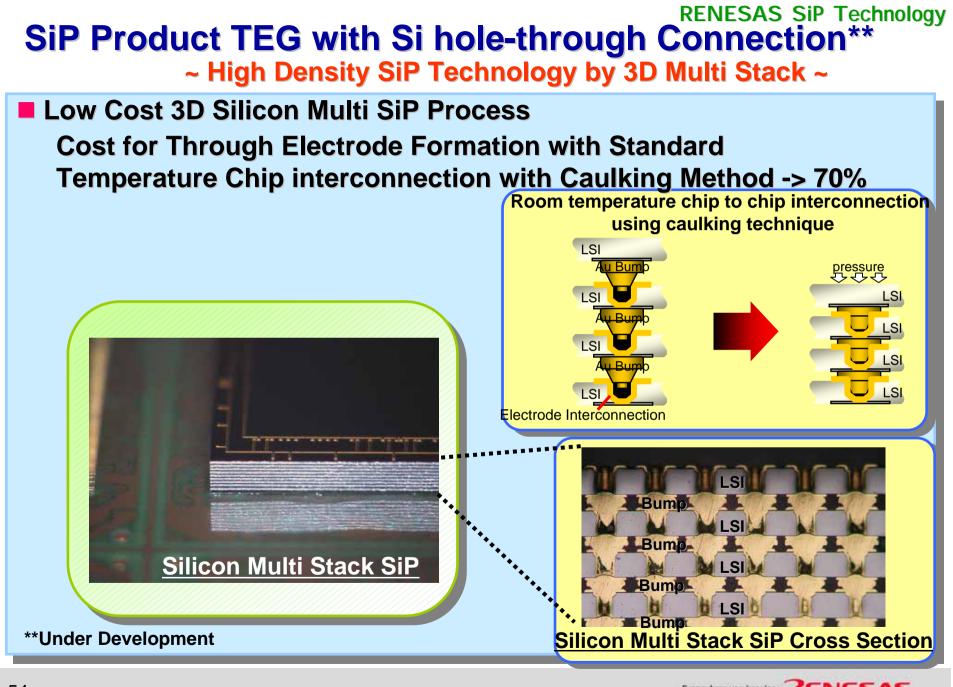

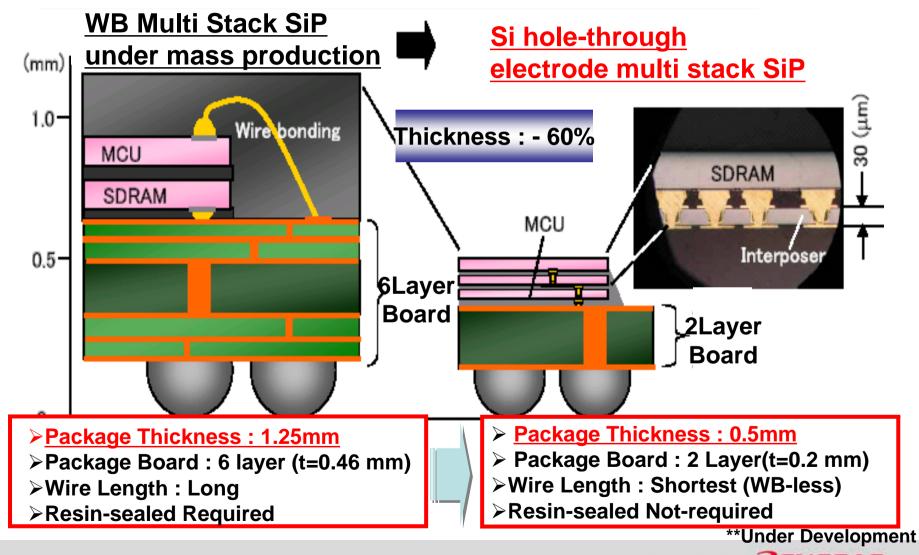

## 11. Next Generation SiP Technology (Si Hole-through Technology)

~ Technology for Ultra thin multi stack SiP ~

## Development of Si Hole-through connection Technology\*\*

54 2006/09/14

## Realize Small/Think making with Si hole-through connection\*\*

### **SiP Roadmap**