#### 先端CMOSアナログ集積回路の課題と今後の展開

CMOSによる回路実現を前提として....

#### 大阪大学 谷口研二

#### 概要

I.MOSFETを用いた増幅回路 Ⅱ.高速アナログ回路設計のポイント Ⅲ.CMOSアナログ回路のレイアウト

常にMOSFET構造を意識しながら.....

# I.MOSFETを用いた増幅回路

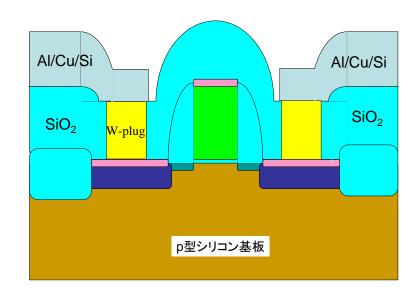

- 1. MOSFETの基本構造

- 2. MOS素子を用いた増幅回路

- 3. 増幅回路の周波数特性

- 4. 半導体ロードマップと新構造デバイス

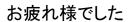

#### CMOSアナログ回路の電源電圧の推移

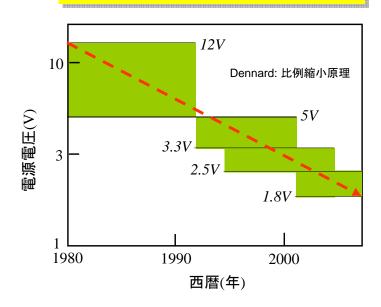

#### 1.MOSFETの基本構造

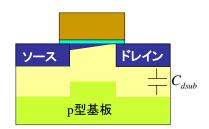

(ゲート電極) 多結晶シリコン 側壁酸化膜 素子間分離酸化膜 高濃度不純物層 ドレイン

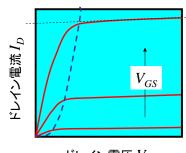

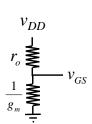

# 出力抵抗 $r_o$ と相互コンダクタンス $g_m$

(アナログ回路にとって重要な2つのパラメータ)

$$I_D = \frac{\beta}{2} \left( V_{GS} - V_T \right)^2 \left( 1 + \lambda V_{DS} \right)$$

ドレイン電圧

$$V_{DS}$$

$$r_o = \left(\frac{dI_D}{dV_{DS}}\right)^{-1} \approx \frac{1}{\lambda I_D}$$

$$dI_D = \sqrt{2} \, dI_D$$

$$g_{m} = \frac{dI_{D}}{dV_{GS}} \approx \sqrt{2\beta I_{D}}$$

ポイント: バイアス電流/<sub>D</sub>の関数

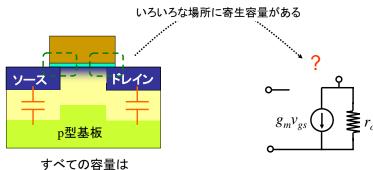

#### MOSFETの寄生容量

(MOSFETの詳細な小信号モデル)

電位に依存する

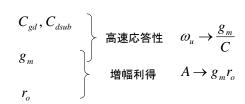

#### --- 高速動作の鍵 ---

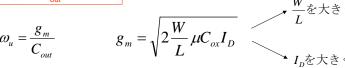

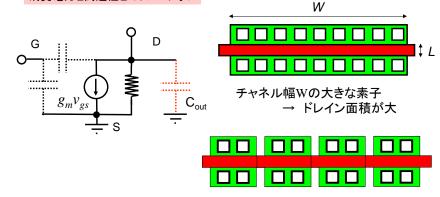

- ①gmの大きな素子を用いる

- ②負荷容量Contを低減する

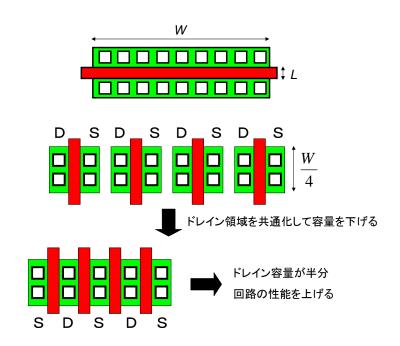

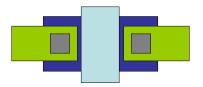

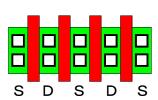

#### チャネル幅Wの大きな素子のレイアウト

#### 消費電力と高速性とのトレードオフ

#### MOSFETのデバイスパラメータ

まとめると....

#### 目安(最先端技術)

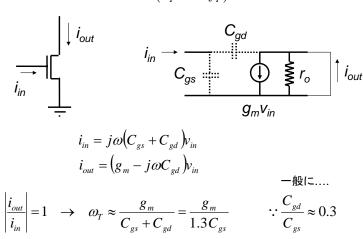

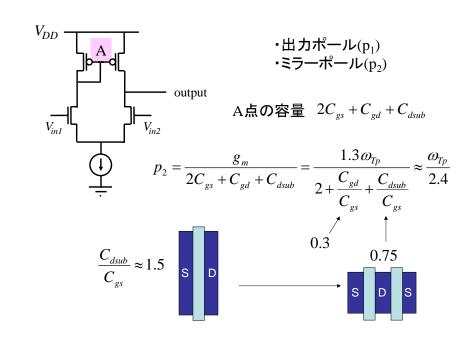

$$\frac{C_{gd}}{C_{gs}} \approx 0.3$$

$$\frac{C_{dsub}}{C_{as}} \approx 1.5$$

#### MOSFETの微細化

素子の微細化によってg<sub>m</sub>, r<sub>o</sub>, Cはどのように変化するのか

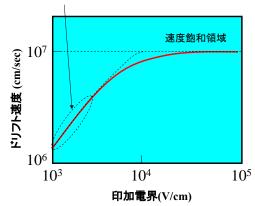

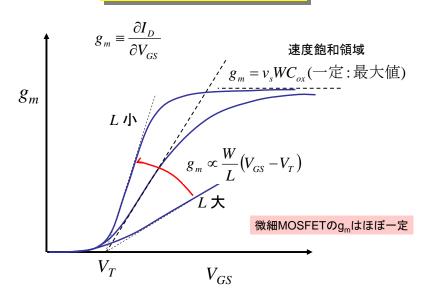

# 素子が小さくなると....ドリフト速度の飽和

オームの法則適用領域

素子内の平均電界

$$\frac{1.5V}{0.15 \, \mu m} = 10^5 \, V \, / \, cm$$

#### 長チャネル*MOSFET*

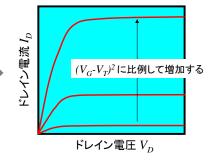

$$I_{Dsat} = \frac{W}{2L} \mu_o C_{ox} (V_{GS} - V_T)^2$$

#### 短チャネルMOSFET

$$I_{Dsat} = \frac{W\mu_{o}C_{ox}(V_{GS} - V_{T})^{2}}{2L[1 + \theta(V_{GS} - V_{T})]}$$

より一般的な式

ドレイン電圧  $V_D$

#### 長チャネルMOSFET

$$I_{Dsat} = \frac{W}{2L} \mu_o C_{ox} (V_{GS} - V_T)^2$$

ドレイン電圧  $V_D$

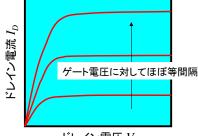

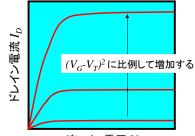

# g<sub>m</sub>のゲート電圧依存性

# 電気的特性のまとめ

#### 短チャネルMOSFET

n=0.8~0.5

$$r_o = \left(\frac{dI_D}{dV_{DS}}\right)^{-1} \approx \frac{1}{\lambda I_D^n}$$

$$g_m = \frac{dI_D}{dV_{GS}} \approx v_s W C_{ox} \quad -$$

$$\omega_u o rac{g_{_m}}{C}$$

微細化が鍵  $I_D$  に依存しない

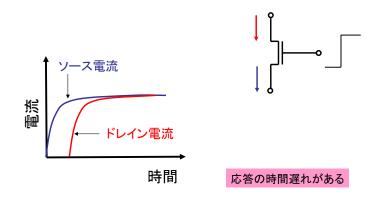

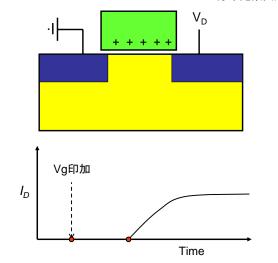

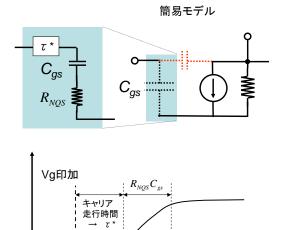

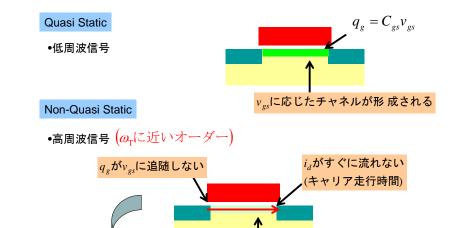

### MOSFETの非平衡輸送現象

究極の高速回路を設計を行う際に考慮すべきポイント NQS(Non-Quasi-Static)効果

## MOSFETの非平衡輸送

分布定数回路

#### MOSFETの非平衡輸送

Time

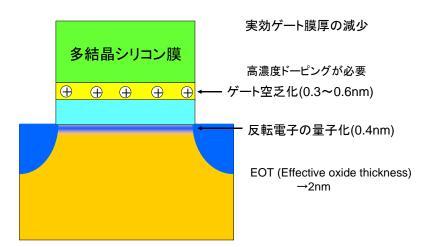

# 半導体ロードマップ

|        | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 | 2012 |                       |

|--------|------|------|------|------|------|------|------|-----------------------|

| ゲート長   | 65   | 53   | 45   | 37   | 32   | 28   | 20   | nm                    |

| EOT    | 2.1  | 2.1  | 1.9  | 1.6  | 1.5  | 1.4  | 1.2  | nm                    |

| ゲート空乏  | 0.8  | 0.7  | 0.7  | 0.7  | 0.4  | 0.4  | 0.4  | nm                    |

| ゲートリーク | 0.5  | 0.9  | 1.5  | 2.2  | 3.1  | 4.8  | 10   | 0.01A/cm <sup>2</sup> |

| オフリーク  | 10   | 15   | 20   | 25   | 30   | 40   | 60   | pA/um                 |

| 移動度増大  | 1.0  | 1.0  | 1.0  | 1.0  | 1.3  | 1.3  | 1.3  |                       |

| 飽和速度増大 | 1.0  | 1.0  | 1.0  | 1.0  | 1.0  | 1.0  | 1.0  |                       |

| 相対性能   | 1.17 | 1.42 | 1.64 | 1.88 | 2.39 | 2.64 | 4.10 | 基準2003年               |

メタルゲートFD-SOI

#### NQS(Non-Quasi-Static)効果のまとめ

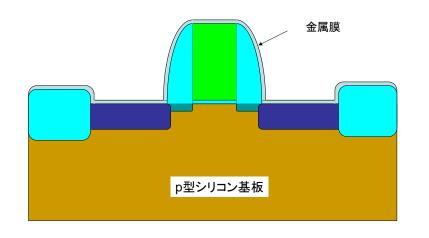

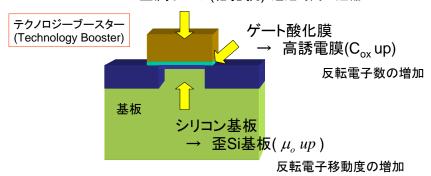

# MOSFETの改良(手軽版)

$i_d$ が $v_{gs}$ に追随しない(信号遅延)

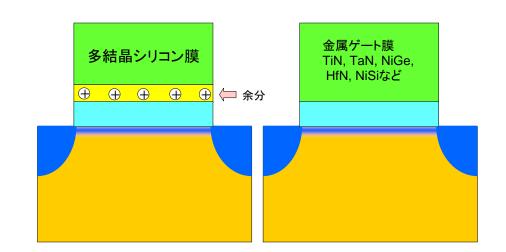

(2007年頃までに....)

多結晶シリコンゲート → 金属ゲート(低抵抗) 遅延時間の短縮

# なぜ金属ゲート?

# なぜ金属ゲート?

- 1. デュアルメタル P-MOS,n-MOS

- 2. シングルメタル

- 3. シリサイド

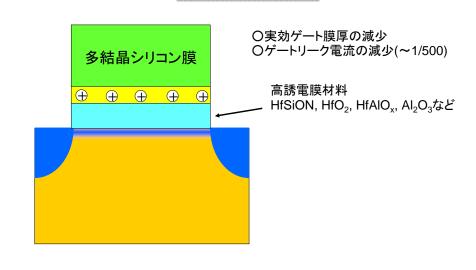

# なぜ高誘電膜?

# 高誘電膜の問題点

高誘電膜材料 HfSiON, HfO $_{2}$ , HfAlO $_{x}$ , Al $_{2}$ O $_{3}$ など

#### 問題点

- 1. 移動度の低下(50%~95%)

- 2. Boronの突き抜け(CVD堆積膜)

- 3. 微量酸素雰囲気中の熱処理で 低誘電率層がHigh-k/Si界面に 形成される。

#### 防止策:

Si

Ge

バリア層(Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>)の使用

- 4. 高温熱処理が困難 (アモルファス→結晶)

- 5. フェルミレベル・ピニング (しきい値が高め)→ 金属ゲート材料

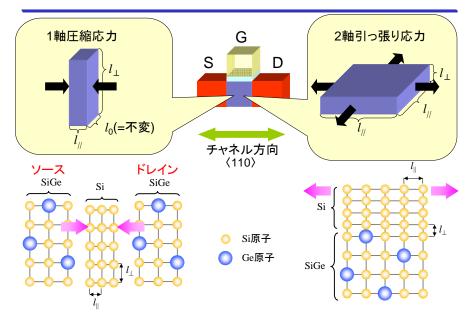

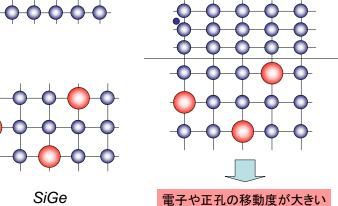

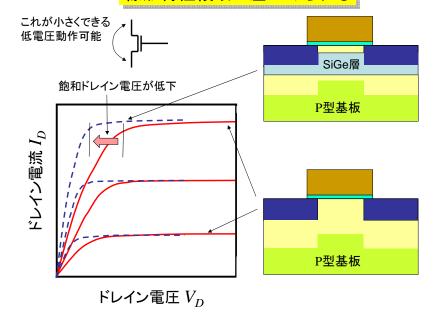

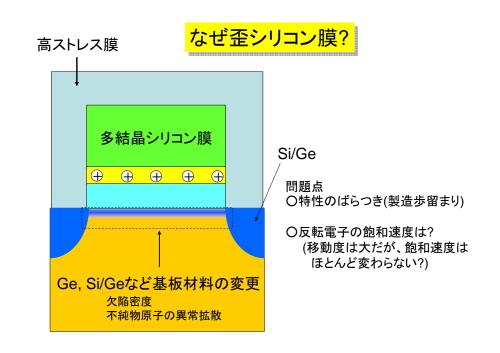

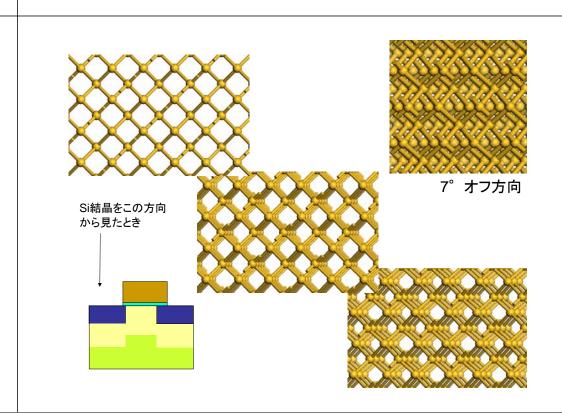

# ひずみの印加方法

#### <mark>ひずみSi膜(Strained Si)</mark>

·結晶構造

·格子間隔

ひずみSi

→ 電気が流れ易い

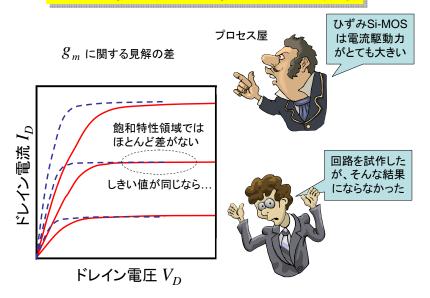

# 線形特性領域に差がみられる

#### プロセス技術者と回路技術者と間の誤解

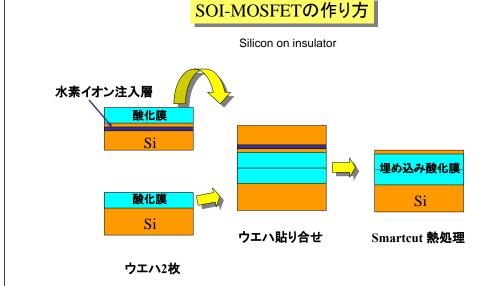

# 将来の新構造デバイス

- 1. SOI MOSFET

- 2. ソース・ドレイン領域を工夫したデバイス

- 3. マルチゲート構造

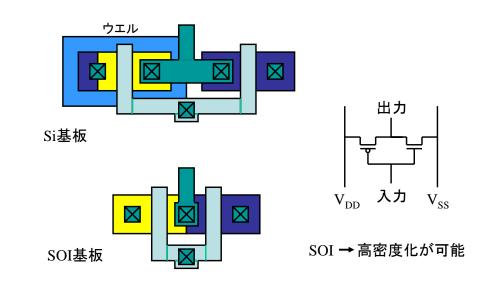

# SOI-MOSFETの占有面積は小さい(1) (素子間分離が容易) n-MOSFET p-MOSFET p-MOSFET p型基板 マスク枚数減 Latch-up free

#### SOI-MOSFETの占有面積は小さい(2) (ウエルが不要)

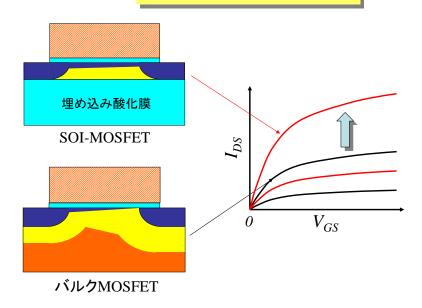

#### SOI-MOSFETの電流駆動力

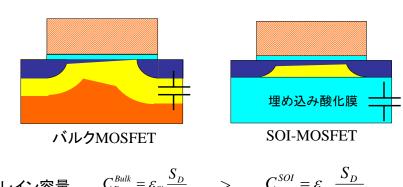

#### SOI-MOSFETはドレイン容量が小さい (高速動作に適している)

ドレイン容量

$$C_D^{Bulk} = \varepsilon_{Si} \frac{S_D}{d_{Si}}$$

$>$   $C_D^{SOI} = \varepsilon_{ox} \frac{S_D}{t_{SiO_2}}$

# Ⅱ.高速アナログ集積回路設計のポイント

- 1.素子のマッチング(入力差動対)

- 2.オペアンプの最大GBWについて

- 3.PSRR(Power Supply Rejection Ratio)

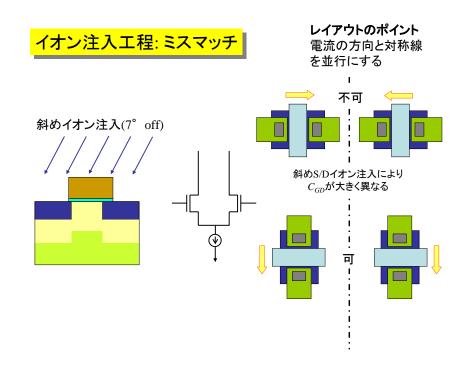

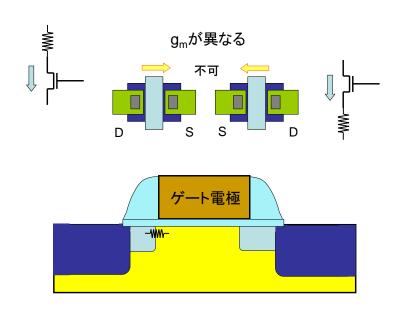

#### 1.素子特性のミスマッチの要因

- ○系統的に特性がばらつく

- ○ランダムな統計的ばらつき

- 2.ミスマッチを軽減する方法

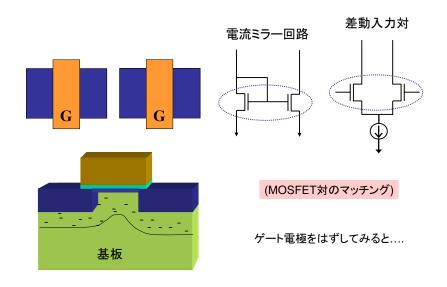

# 1.MOS素子のマッチング

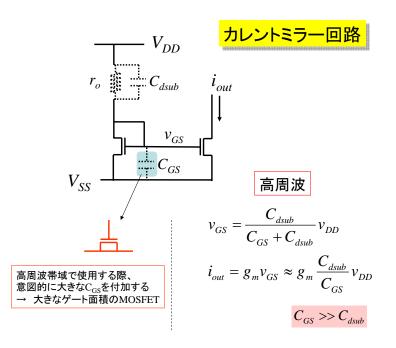

カレントミラー回路

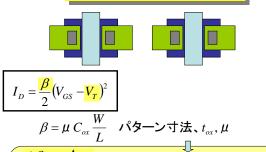

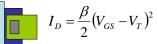

$I_D = \frac{\beta}{2} (V_{GS} - V_T)^2$

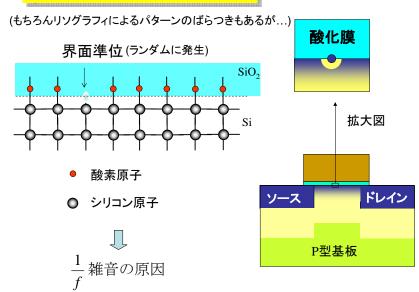

#### ランダムな統計的ばらつき

#### 不純物原子数のゆらぎが原因

K.R.Laksmlkumar, R.A.Hadaway, and M.A.Copeland, "Characterization and Modeling of Mismatch in MOS transistors for Precision Analog Design," IEEE Journal of Solid State Circuits, SC-21, 1057 (1986).

M.J.M.Pelgrom, A.C.J.Duinmaijer, and A.P.G.Welbers, "Matching Properties of MOS transistors," IEEE Journal of Soilid-State Circuits, SC-24, 1433 (1989)

#### β値ばらつきの微視的な原因

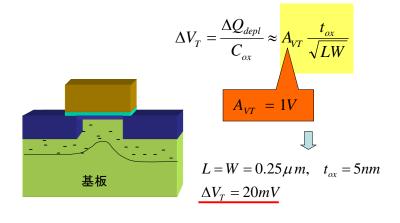

#### MOSFET対の精度

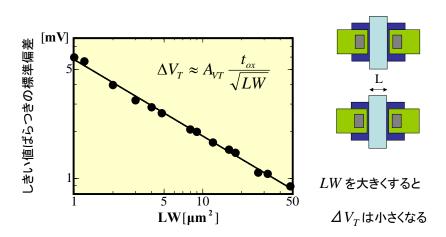

# しきい値ばらつきのゲート面積依存性

#### しきい値のばらつき ---統計的な不純物原子数のゆらぎ---

T.Mizuno, J.Okamura and A.Toriumi, "Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFETs," IEEE Trans. On Electron Devices, ED-41, 2216 (1994)

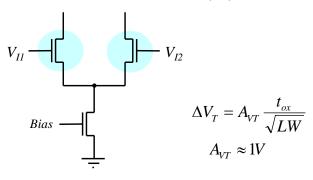

# 入力オフセット電圧を小さくするには

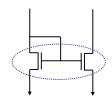

# 入力差動対

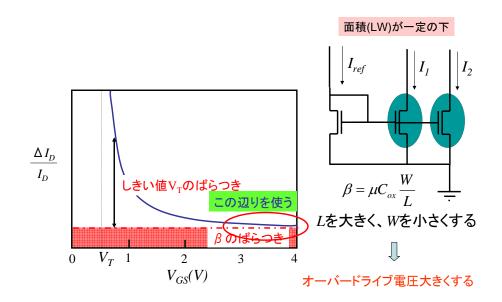

面積(LW)が一定の下

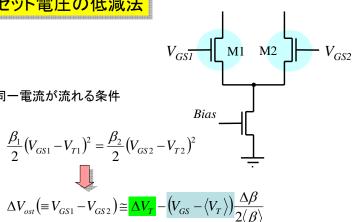

### オフセット電圧の低減法

M1, M2に同一電流が流れる条件

ゲート面積LWを大きくする  $\rightarrow \Delta V_T$ が小さくなる

W/Lを大きくする  $\rightarrow V_{GS}$ - $V_T$ が小さくなる

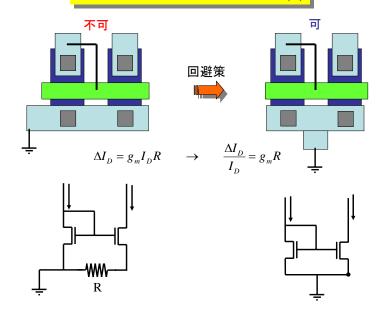

#### カレントミラー回路の電流ミスマッチの低減法

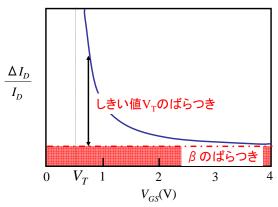

しきい値 $V_T$ と $\beta$ 値の双方が影響する

$$\frac{\Delta I_D}{I_D} = \sqrt{4 \left(\frac{\Delta V_T}{V_{GS} - V_T}\right)^2 + \left(\frac{\Delta \beta}{\beta}\right)^2}$$

### 電流ミスマッチを小さくするには(2)

# カレントミラー回路の配置法(1)

#

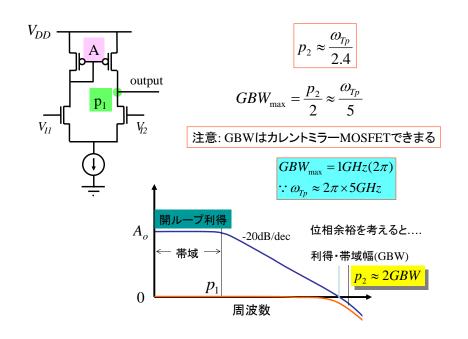

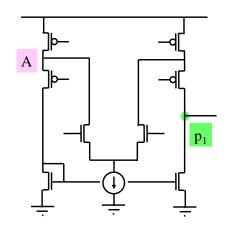

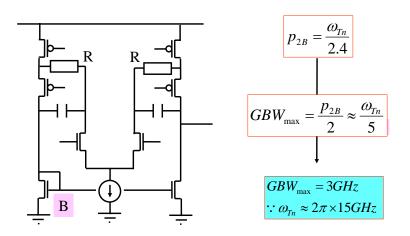

# 2. オペアンプの最大GBWについて

与えられたTechnologyの下で.... 最高速オペアンプを実現するには

#### MOSFETの遮断周波数

$$(\omega_T = 2\pi f_T)$$

$:: \omega_{Tp} \approx 2\pi \times 5GHz$

#### pチャネルMOSFETをバイパス

# さらに大きなGBWを得るには...

(信号経路にカレントミラーを避ける)

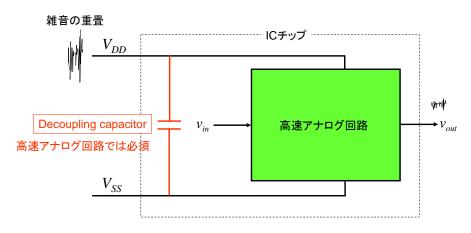

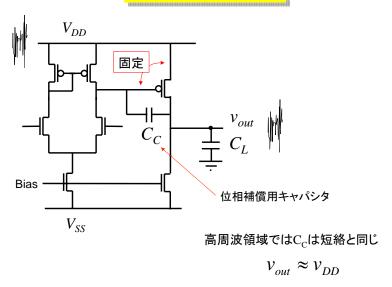

#### 4.PSRR(Power Supply Rejection Ratio)を確保するには

#### 高周波領域では寄生容量が問題

PSRR (Power Supply Rejection Ratio)

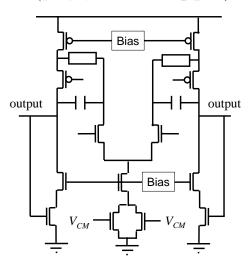

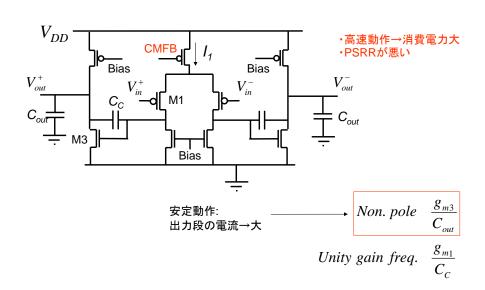

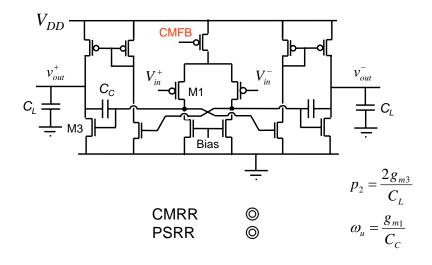

#### <mark>一般的な全差動オペアンプ</mark>

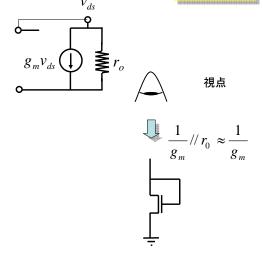

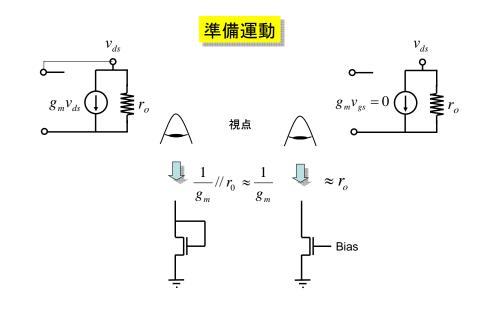

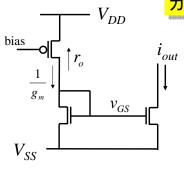

#### 準備運動

#### 低周波

$$v_{GS} = \frac{\frac{1}{g_m}}{r_o + \frac{1}{g_m}} v_{DD} \approx \frac{1}{g_m r_o} v_{DD}$$

$$i_{out} = g_m v_{GS} \approx \frac{v_{DD}}{r_o}$$

対策: 出力抵抗を大きくして 電源電圧変動の影響を

抑制する

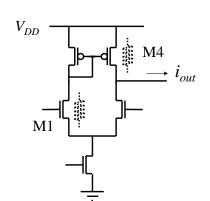

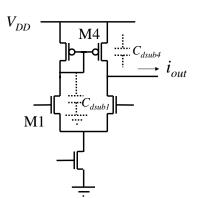

#### <mark>差動アンプ</mark>

#### 低周波

$$i_{out} \approx \left(\frac{1}{r_{o1}} + \frac{1}{r_{o4}}\right) v_{DD}$$

対策: 出力抵抗を大きくして 電源電圧変動の影響を 抑制する

$$i_{out} \approx j\omega (C_{dsub4} + C_{dsub1}) v_{DD}$$

対策: ドレイン容量を小さくして 電源電圧変動の影響を 抑制する

# 出力段を接続すると

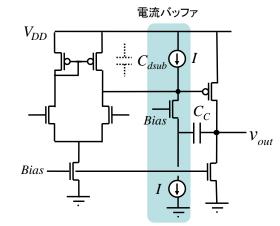

# 電流バッファを挿入

高周波領域では....

$$sC_C v_{out} = sC_{dsub} v_{DD}$$

$$v_{out} = \frac{C_{dsub}}{C_C} v_{DD}$$

$C_C$  位相補償用キャパシタ

# 全差動構成だと....

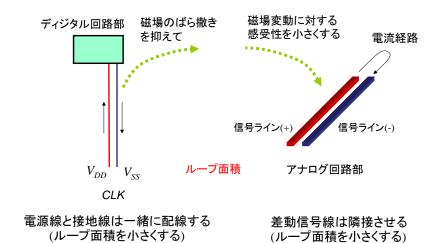

# Ⅲ.高速アナログ集積回路のレイアウト

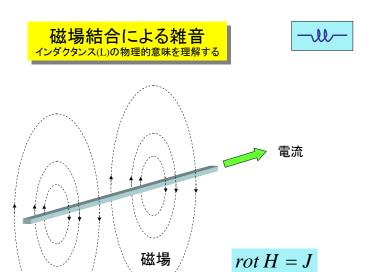

- 1. 磁場結合による雑音

- 2. 基板抵抗結合による雑音

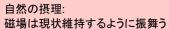

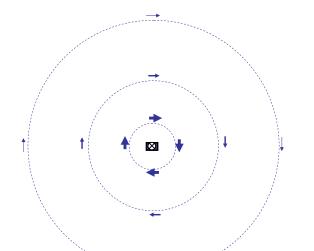

# 電磁誘導とは

-W-

$V_2 = -M_{21} \frac{dI_1}{dt}$ 相互インダクタンス

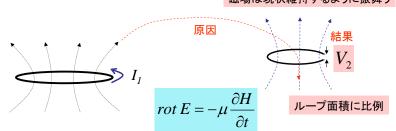

# 電磁誘導(L)による雑音

磁場

直線配線でも発生する

電流を流すと....配線の周囲に磁場を撒き散らす

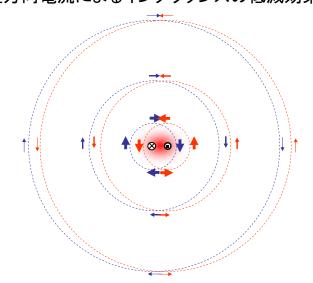

### 逆方向電流によるインダクタンスの低減効果

# **逆方向電流によるインダクタンス** □-٫↓↓/--

逆方向電流: 周囲に磁場を撒き散らさない

### 電磁誘導を抑えるには

電磁誘導を軽減

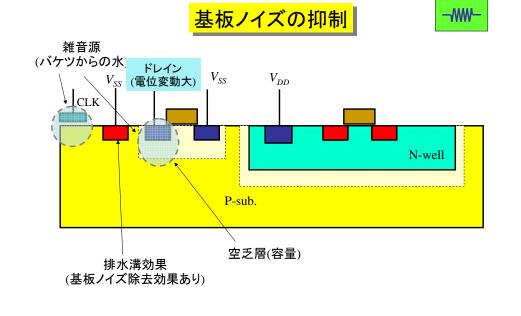

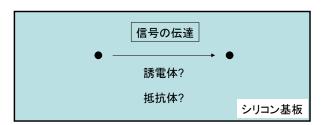

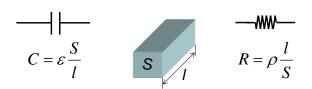

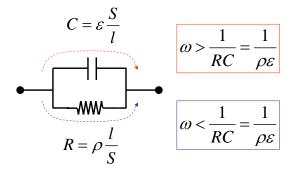

# 基板抵抗結合による雑音

| $\rho(\Omega cm)$ | $f_t(GHz)$ |

|-------------------|------------|

| 10-2              | 15000      |

| 10º               | 150        |

| 10 <sup>2</sup>   | 1.5        |

$f_t$ 以下の周波数では シリコン基板:  $\rightarrow$  抵抗体

**-**WW-

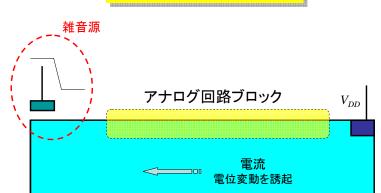

# 基板(経由)雑音について

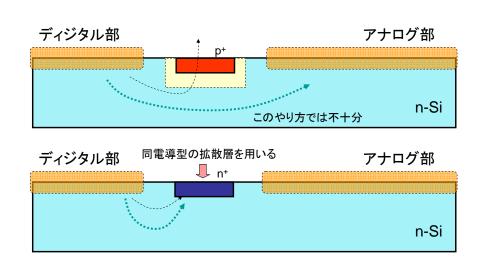

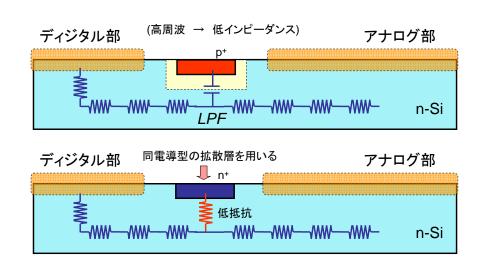

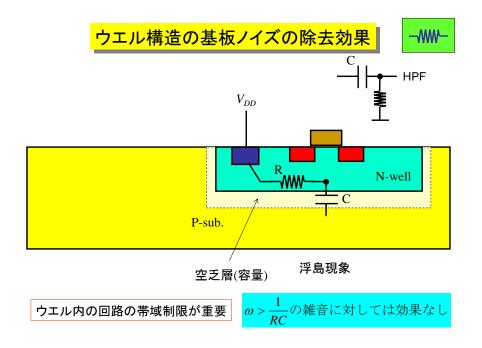

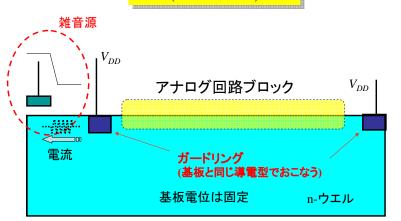

# 雑音経路の遮断方法

# ガードリングの配置

n-ウエル

-WW-